[5] Verilog HDL 모듈, 테스트 벤치

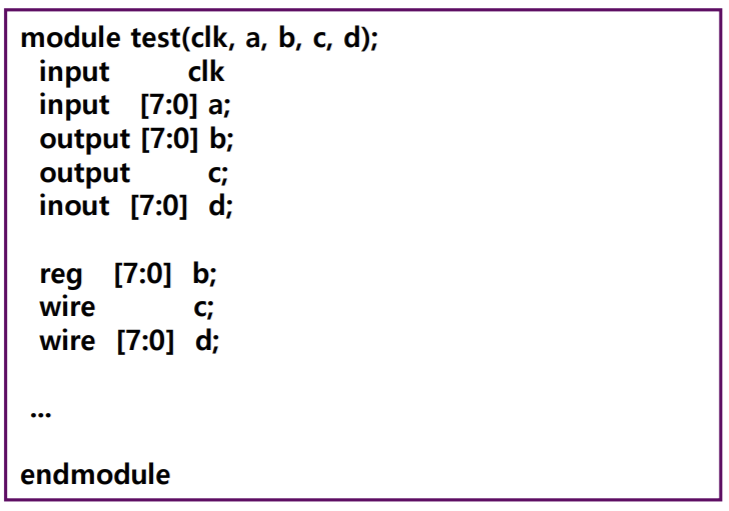

Verilog의 모듈과 포트선언

- 포트목록(port_list)에는 입력, 출력, 입출력 신호를 열거합니다.

- 포트 선언부에서 input, output, inout(양방향) 중 하나로 선언하고 이때 비트 수도 명시합니다.

- output과 inout에 대해서는 reg 또는 wire정의가 같이 있을 수 있습니다.

- input에 대해서는 기본적으로 wire이므로 다시 정의할 필요가 없습니다.

모듈의 포트 선언

- 몇가지 스타일의 포트를 선언할 수있습니다. 왼쪽이 standard입니다.

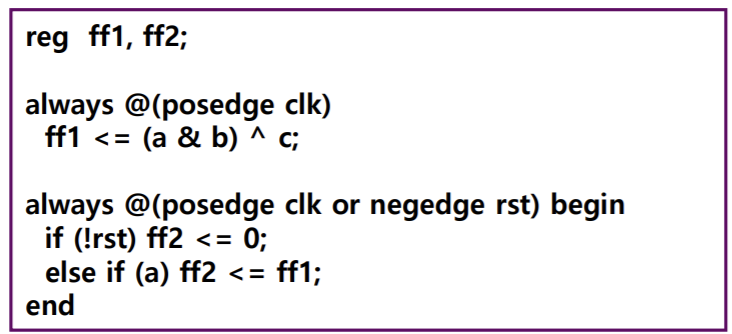

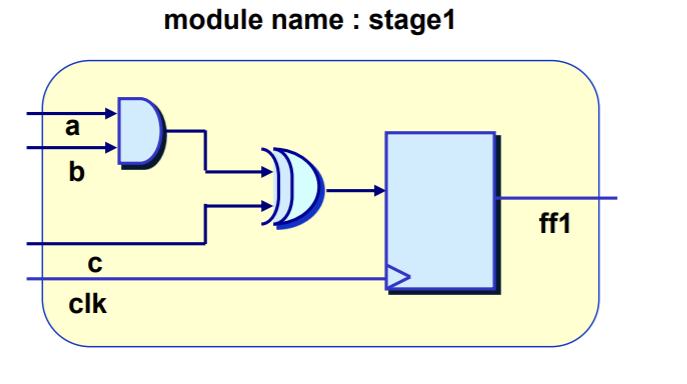

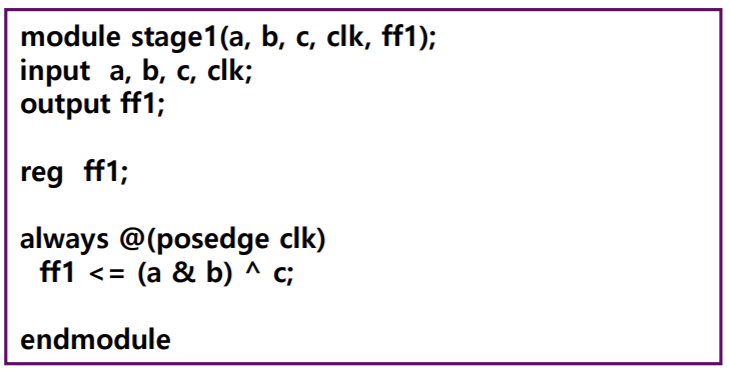

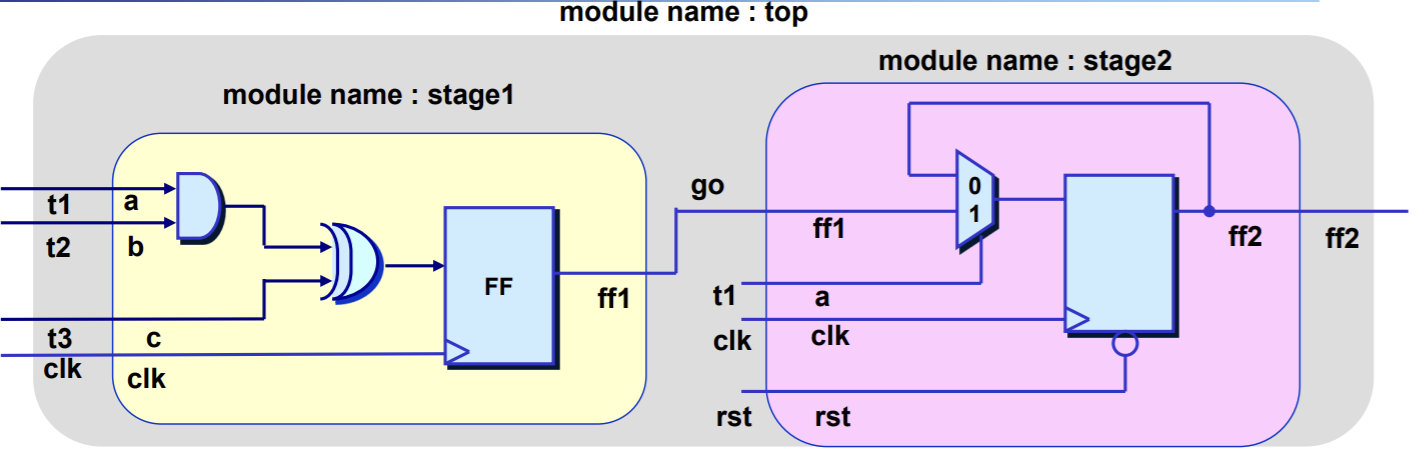

모듈 분할

왼쪽과 오른쪽 모듈을 각각 따로 생각하여 HDL을 작성할 수 있습니다.

하위 모듈 : stage1

하위 모듈 : stage2

상위 모듈 : top

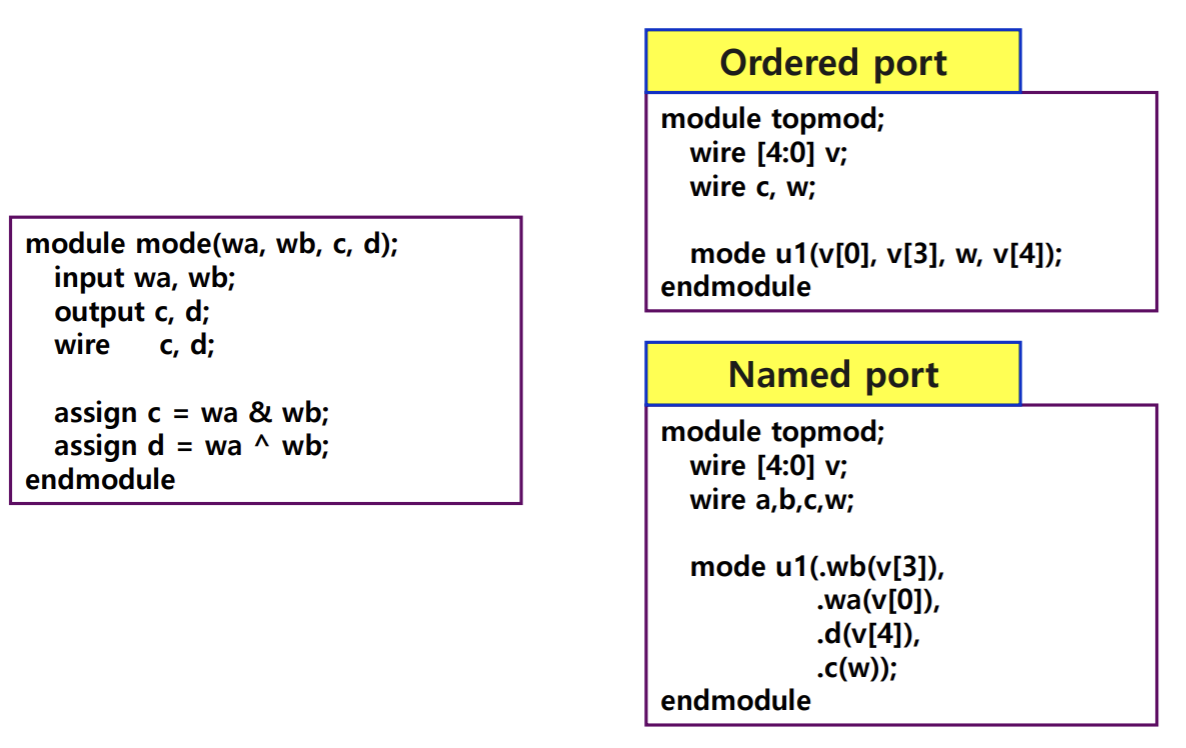

모듈 인스턴스(instantiation) 방법

- 포트순서에 의한 포트 매핑 (ordered port)

- 모듈의 포트목록에 나열된 포트 순서와 일대일 대응되어 연결합니다.

- 포트에 연결되는 신호가 없는 경우에는 해당 위치를 빈칸으로 남겨둡니다.

- 주로 Test bench에서 사용합니다.

- 포트이름에의한 포트 매핑(named port)

- 포트 이름과 그 포트에 연결되는 신호 이름을 명시적으로 지정합니다.

- 포트의 비트 선택, 부분 선택, 결합 등을 사용할 수 없습니다.

- DUT에서 주로 사용합니다.

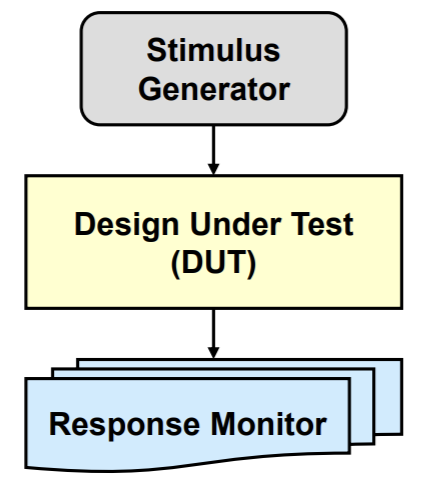

테스트 벤치(Test bench)

- DUT를 시뮬레이션하기 위한 Verilog 모듈

- DUT에 인가될 시뮬레이션 입력(stimulus)를 생성하는 구문입니다.

- 시뮬레이션 대상이 되는 모듈(Design Under Teset ; DUT)의 인스턴스

- 시뮬레이션 입력에 대한 DUT의 반응(response)을 관찰하는 구문

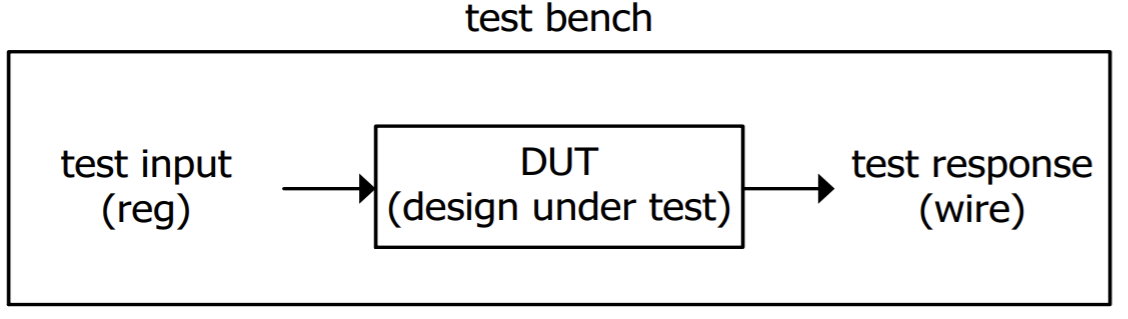

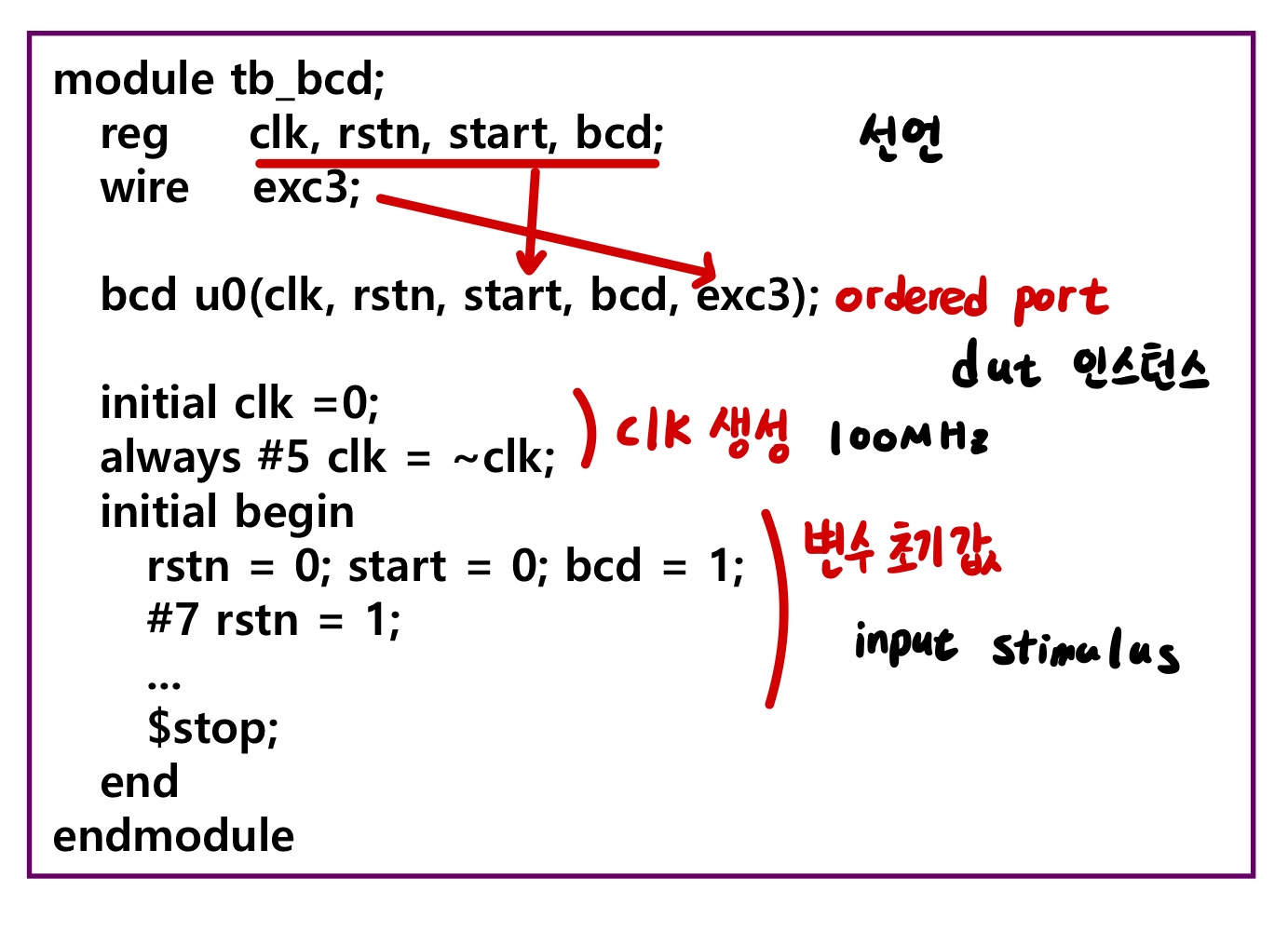

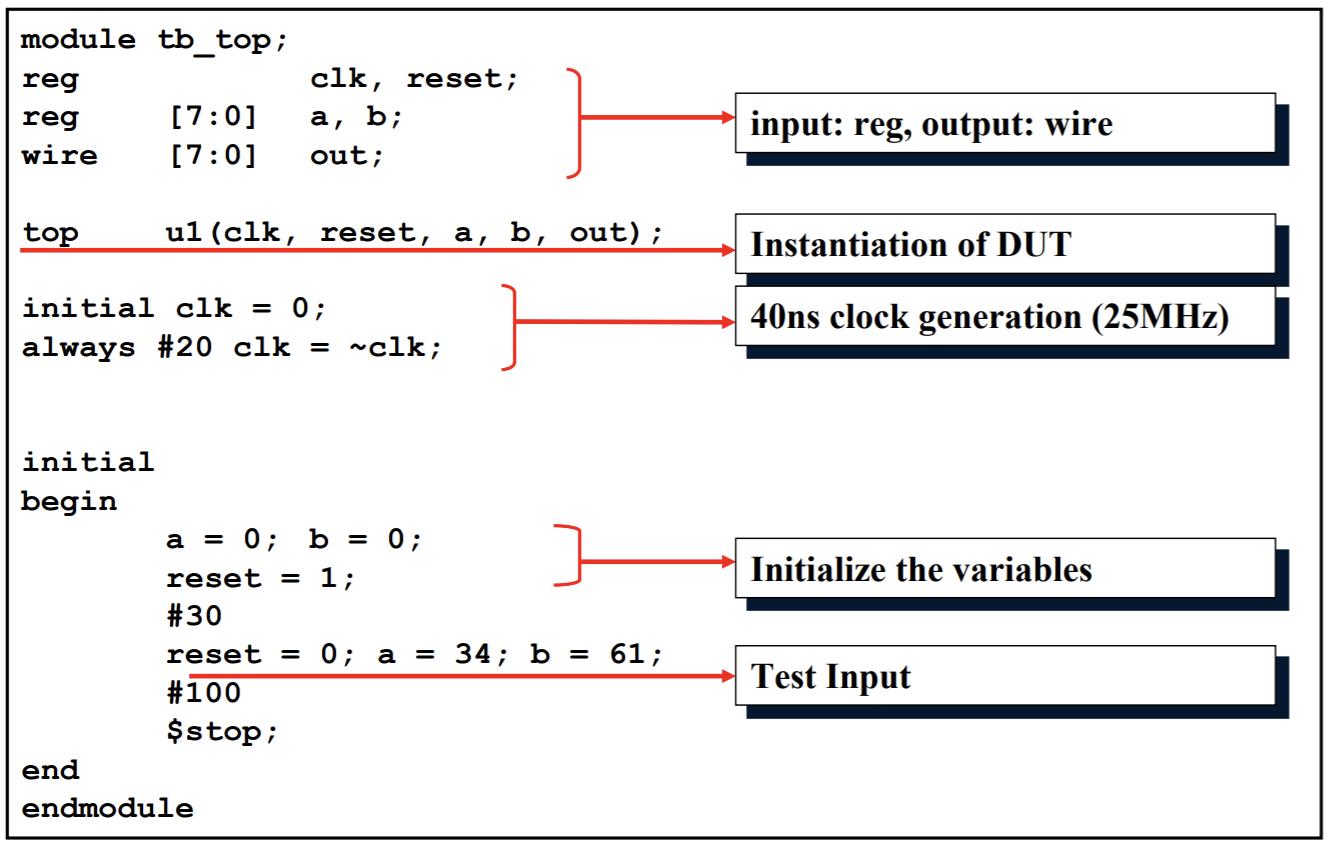

Test Bench module

- 신호선언

- test input : reg 선언, 보통 always나 initial을 사용하여 신호를 발생시킨다.

- test output : wire 선언, 선언만 하고 사용하지 않아도 됨

- 특징

- 일반적으로 가장 상위의 모듈로 입출력이 없다.

- 합성이 필요하지 않은 블록으로 간으한 모든 Verilog 문장을 사용할 수 있습니다.

Initial 구문

- 시뮬레이션이 시작되면서 한번만 실행되는 구문

- 할당문들은 보통 blocking 할당문을 사용

- 문장들은 나열된 순서대로 실행

- 논리합성이 지원되지 않는다.

지연시간 기호 #

- DUT에서는 사용하지 않는다.

wait 문

- wait문의 조건을 평가

- 참이면 다음 문장을 실행

- 거짓이면 계속 대기

- wait문장은 합성이 불가합니다.

이벤트(event)기호 @

- @기호는 이벤트(event)를 기다리는 기호

- DUT의 always구문에서 자주 사용합니다.

- always없이 테스트 벤치에서 단독으로 사용가능합니다.

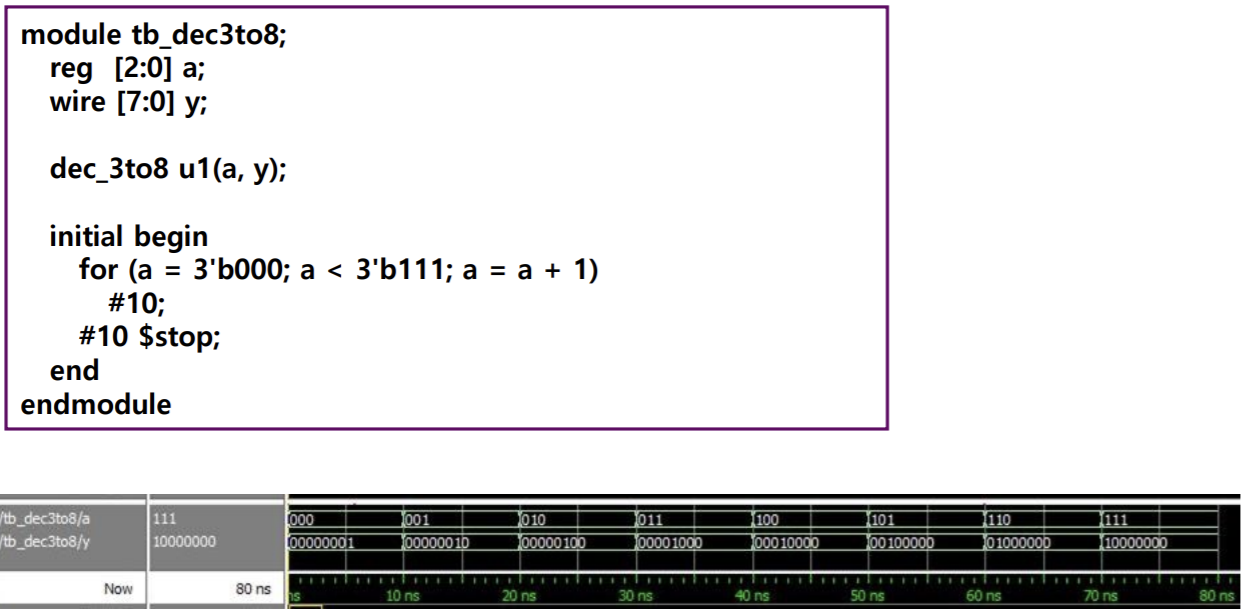

테스트 벤치의 예

8bit adder와 테스트 벤치

반복문 for

- a++과 같은 표현은 사용하지 못합니다.

블록문

- 두 개 이상의 문장을 그룹으로 묶어 구문적으로 하나의 문장처럼 처리합니다.

- begin - end 절차형 할당문 블록

- 문장이 나열된 순서에 의해 순차적으로 실행

- fork - join 병렬문 블록

- 문장의 나열 순서에 무관하게 동시에 실행

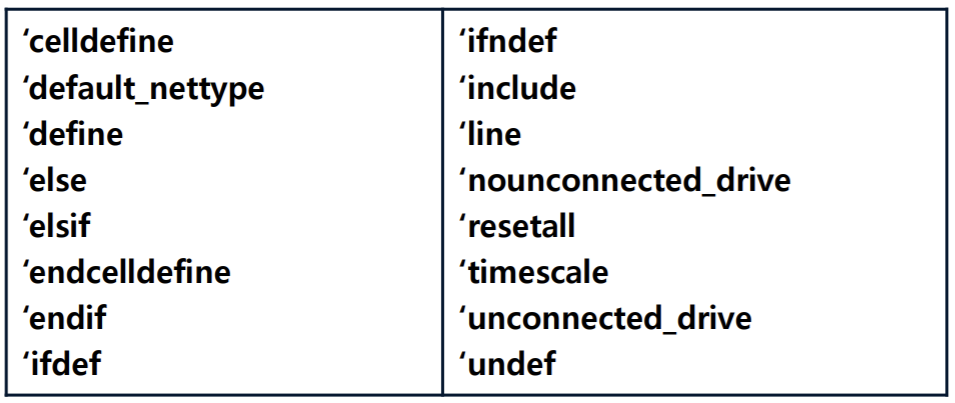

컴파일러 지시어

- Verilog 소스코드의 컴파일 과정에 영향을 미치는 명령어

- ' 으로 시작함 .

- 파일내의 모든 곳에 위치간으하나 일반적으로 모듈 정의 위에 위치합니다.

`ifdef, `ifndef, `elsif, `else, `endif

- verilog 소스코드의 일부를 조건적으로 컴파일하기위해 사용합니다.

`ifdef : 매크로 이름이 정의되어 있으면, ‘ifdef 이후의 소스코드가 컴파일 됨

`ifndef : 매크로 이름이 정의되어 있지 않으면, ‘ifndef 이후의 코드가 컴파일 됨

`elsif : `ifdef 또는 `ifndef 조건이 맞지 않을 경우 다시 조건을 조회하여 컴파일

`else : `ifdef 또는 `ifndef 조건이 맞지 않을 경우 `else 이후가 컴파일 됨

`endif : 조건적으로 컴파일되는 소스코드의 경계를 나타냄

만약 behavioral이 정의되어있으면 wire a = b&c 이 구문 실행

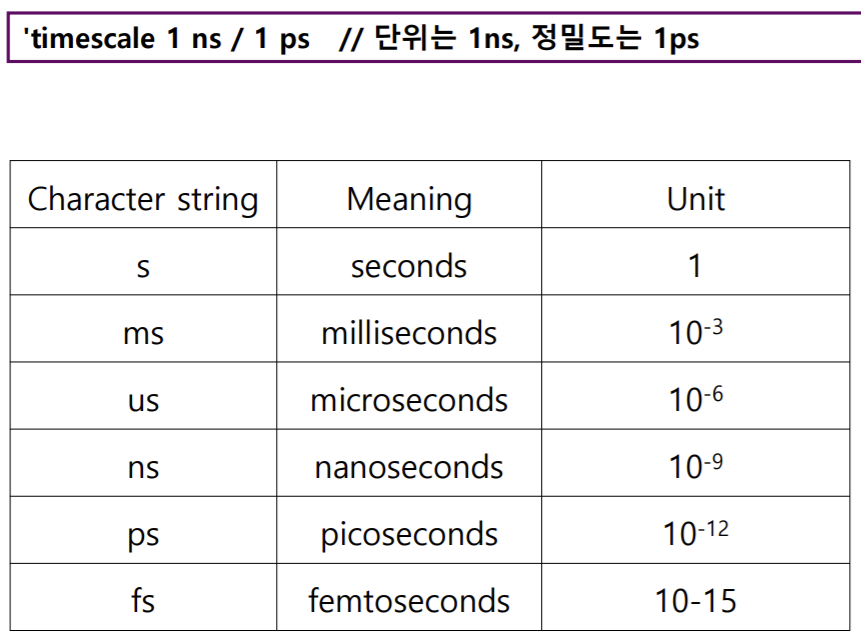

timescale

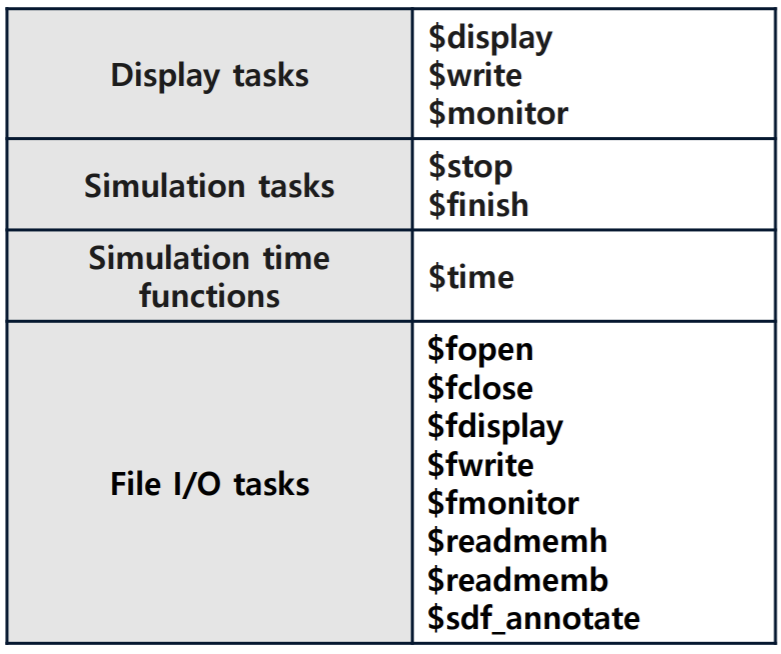

시스템 Task

- 주요 시스템 task

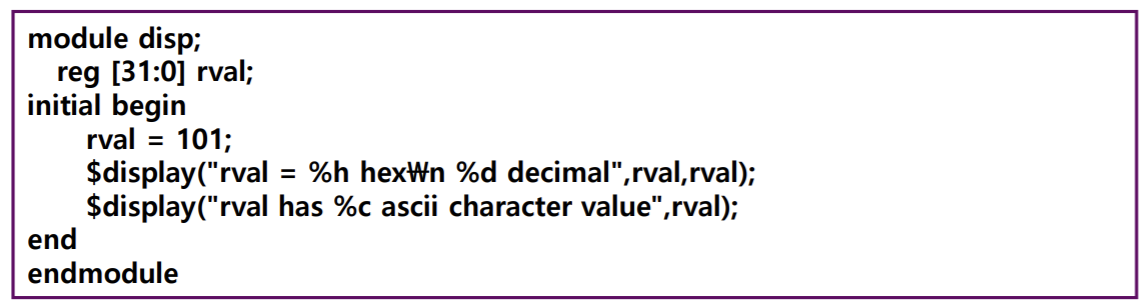

$display

- 줄바꿈 문자가 자동으로 삽입됩니다.

$display 출력형식