![[18] Verilog HDL 조합회로 구현(NAND, NOR, BOOL, TRUTH TABLE, MUX)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FvkaG2%2FbtruTEU4zA8%2FAAAAAAAAAAAAAAAAAAAAAMf1KEg2Oe8FhXPunXtmmwxGoVogRSJ8qPW1hQ9Qp_JR%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1774969199%26allow_ip%3D%26allow_referer%3D%26signature%3DGX%252F%252FwZ%252BrpVoAg91GOfI6marrwIc%253D)

조합회로

조합논리회로는 현재 인가되고 있는 입력에 의해서만 출력이 결정되는 회로이며, 과거의 입력이나 출력, 현재 상태 등을 저장하는 소자(래치, 플립플롭)를 포함하지 않는 회로이다. 디지털 시스템 설계에는 기본 논리 게이트부터 멀티플렉서, 인코더/디코더, 가산기/감산기, 등의 기능블록, lookup테이블 및 랜덤 로직 등 매우 다양한 조합논리회로들이 사용된다.

★ 조합논리회로의 올바른 HDL 모델링을 위한 유의사항

① always구문을 이용한 행위수준 모델링에서 always블록의 감지신호 목록에 회로의 입력신호들이 빠짐없이 들어가야한다.

② if 조건문과 case문에서 모든 입력 조건들에 대한 출력값이 명시적으로 지정되어야 한다. 만약 그렇지 안은 경우에는 논리합성 과정에서 래치가 생성되어 조합논리회로가 아닌 순차논리회로가 생성될 수 있다.

★ 기본 논리게이트의 HDL 모델링

기본 논리게이트의 HDL모델링에는 비트 연산자, 게이트 프리미티브, if 조건문 등의 구문이 사용될 수 있다. 다음은 4 입력 NAND게이트를 다양한 방법으로 모델링 한 것이다.

방법 1 : 단항 연산자인 축약 NAND연산자 ~&을 활용해 모델링.

방법 2 : 비트 AND 연산자 &와 부정 연산자 ~을 활용해 모델링.

방법 3 : if 조건문을 사용한 모델링이며, 4입력 NAND게이트의 진리표로부터 출력이 1이되는 조건을 찾아 적용한다. 출력 y는 always블록 내부에서 값을 받으므로 reg형으로 선언되어야 한다.

// 1. 4BIT NAND GATE

module nand4(a,y);

input [3:0] a;

output y;

// 방법1 : 축약연산자.

assign y = ~&a;

// 방법2 : 비트연산자

assign y = ~(a[0]&a[1]&a[2]&a[3]);

// 방법3 : 조건문

reg y;

always @(*) begin

if(a==4'b1111) y=0;

else y=1;

end

endmodule▣ TESTBENCH

// 4BIT NAND GATE TESTBENCH

module tb_nand4;

reg [3:0] a;

wire y;

integer i;

nand4 u0 (a,y);

initial begin

a = 0;

for(i=1;i<32;i=i+1) begin

#20 a = i;

end

end

endmodule

★ 멀티비트 논리연산의 HDL 모델링

4비트 데이터 a[3:0], b[3:0]에 대한 NOR연산은 다음그림과 같으며, 4개의 2입력 NOR게이트로 구현되며, 비트연산자, for반복문 등의 구문으로 모델링할 수 있다.

방법1 : 비트 OR연산자 |와 비트 부정 연산자 ~을 활용한 모델링

방법2 : for반복문을 활용한 모델링이며, 반복회수를 비트 수와 동일하게 지정한다.

// 2. 4BIT 2INPUT NOR GATE

module mulitnor(a,b,y);

input [3:0] a,b,;

output [3:0] y;

integer i;

// 방법1 : 비트 연산자.

assign y = ~(a|b);

// 방법2 : for문

reg y;

always @(*) begin

for(i=0;i<4;i=i+1) begin

y[i] = ~(a[i] | b[i]);

end

end

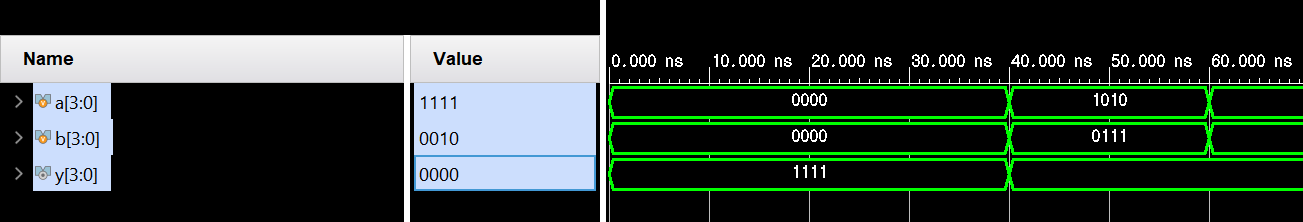

endmodule▣ TESTBENCH

// 4BIT 2INPUT NOR GATE TESTBENCH

module tb_mulitnor(a,b,y);

reg [3:0] a,b;

wire [3:0] y;

mulitnor u0(a,b,y);

initial begin

a = 4'b0000; b = 4'b0000;

#20 a = 4'b0000; b = 4'b0000;

#20 a = 4'b1010; b = 4'b0111;

#20 a = 4'b1111; b = 4'b0010;

#20;

end

endmodule

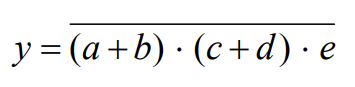

★ 부울 함수의 HDL 모델링

부울 함수로 표현된 임의의 논리식은 비트연산자를 통해 사용하여 모델링할 수 있다. 다음의 부울 함수는 다음 코드와 같이 모델링될 수 있다.

module boolmodeling(a,b,c,d,e,y);

input a,b,c,d,e;

output y;

assign y = ~((a|b)&(c|d)&c);

endmodule▣ TESTBENCH

module tb_boolmodeling;

reg a,b,c,d,e;

wire y;

boolmodeling u0(a,b,c,d,e,y);

initial begin

a=0;b=1;c=0;d=1;e=0;

#20 a=1;b=0;c=1;d=0;e=1;

#20;

end

endmodule

★ 진리표의 HDL 모델링

조합논리회의 기능이 진리표(truth table)로 정의된 경우에는 case문을 이용하여 진리표를 직접 HDL로 표현하는 방법이 사용된다. 다음의 표는 곱셈기 설계에 사용되는 Booth인코딩의 진리표이며, 3비트의 입력을 받아 y,y2,neg를 출력한다.

다음은 case구문을 사용하여 위의 진리표를 구현한 것이다. case(xin)에 의해 입력 xin값에 따른 tmp[2:0]의 값이 결정되고, assign문을 통해 인코딩 결과값 y,y2,neg가 출력된다.

module booth_enc(xin,y,y2,neg);

input [2:0] xin;

output y,y2,neg;

reg[2:0] tmp;

assign y = tmp[2];

assign y2 = tmp[1];

assign neg = tmp[0];

always @(xin) begin

case(xin)

0 : tmp = 3'b000;

1,2 : tmp = 3'b100;

3 : tmp = 3'b010;

4 : tmp = 3'b011;

5,6 : tmp = 3'b101;

7 : tmp = 3'b001;

endcase

end

endmodule▣ TESTBENCH

module tb_booth_enc;

reg [2:0] xin;

wire y,y2,neg;

integer i;

booth_enc u0(xin,y,y2,neg);

initial begin

xin =0;

for(i=1;i<16;i=i+1) begin

#20 xin = i;

end

end

endmodule

★ 멀티플렉서 HDL 모델링

멀티플렉서는 여러 개의 입력 중에서 하나를 선택하여 출력하는 회로이며, if-else, if조건문, case문 조건 연산자 등을 이용하여 모델링할 수 있다. 다음 코드는 4 : 1 멀티플렉서를 if-else문과 case문 2가지 방법을 통해 모델링했다. 두 모델링 모두 동일한 회로로 합성된다.

module mux41(sel,a,b,c,d,y);

// 1. case 사용

input [1:0] sel;

input [3:0] a,b,c,d;

output reg [3:0] y;

always@(*)begin

case(sel)

0 : y=a;

1 : y=b;

2 : y=c;

3 : y=d;

default : y=4'bx;

endcase

end

// 2. if문 사용

input [1:0] sel;

input [3:0] a,b,c,d;

output reg [3:0] y;

always@(*)begin

if(sel==2'b00) y=a;

else if(sel==2'b01) y=b;

else if(sel==2'b10) y=c;

else if(sel==2'b11) y=d;

else y=4'bx;

end

// 3. 조건 연산자 사용.

input [1:0] sel;

input [3:0] a,b,c,d;

output [3:0] y;

assign y = (sel==2'b00)?y=a:(sel==2'b01)?y=b:(sel==2'b10)?y=c:(sel==2'b11)?y=d:y=4'bx;

endmodule

'UVM & RTL > Verilog HDL' 카테고리의 다른 글

| [20] Verilog HDL 조합회로 구현 (ENCODER, DECODER) (0) | 2022.03.05 |

|---|---|

| [19] Verilog HDL 조합회로 설계과제1 (NAND, NOR, BOOL, TRUTH TABLE, MUX) (0) | 2022.03.05 |

| [17] Verilog HDL Inernal Memory Interface 실습 (0) | 2022.01.22 |

| [16] Verilog HDL Inernal Memory Interface (0) | 2022.01.22 |

| [15] Verilog HDL Memory의 종류와 특징 (0) | 2022.01.22 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[20] Verilog HDL 조합회로 구현 (ENCODER, DECODER)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FF6bFT%2Fbtru2vJjTql%2FAAAAAAAAAAAAAAAAAAAAAPYTmcnkSYV18jAsJj7TjVIABauuVOuV-qaDnj8GZ7g_%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1774969199%26allow_ip%3D%26allow_referer%3D%26signature%3DeVy85wMDk5UZVJHvGRwBcTSJg%252Fc%253D)

![[19] Verilog HDL 조합회로 설계과제1 (NAND, NOR, BOOL, TRUTH TABLE, MUX)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbDVQ3D%2Fbtru5cJxlLw%2FAAAAAAAAAAAAAAAAAAAAAF7yXfPE26OnGgiepyz5opZud5lZ3Tg9QrZsMVdnr_nS%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1774969199%26allow_ip%3D%26allow_referer%3D%26signature%3Dg0CLOW83Aovoa6vc%252FKYYwab1uHg%253D)