![[23] Verilog HDL 순차회로 설계과제 (COMPARATOR, TRI-STATE)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FzWmUP%2FbtruI8hYeP4%2FAAAAAAAAAAAAAAAAAAAAACZSlD5I-litRdCYEJ25Io2t15-K0Q4ZPrta8MRGVOJb%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DxBx%252FMmN9SocY1ySw619wXHMYVqs%253D)

[23] Verilog HDL 순차회로 설계과제 (COMPARATOR, TRI-STATE)UVM & RTL/Verilog HDL2022. 3. 5. 19:00

Table of Contents

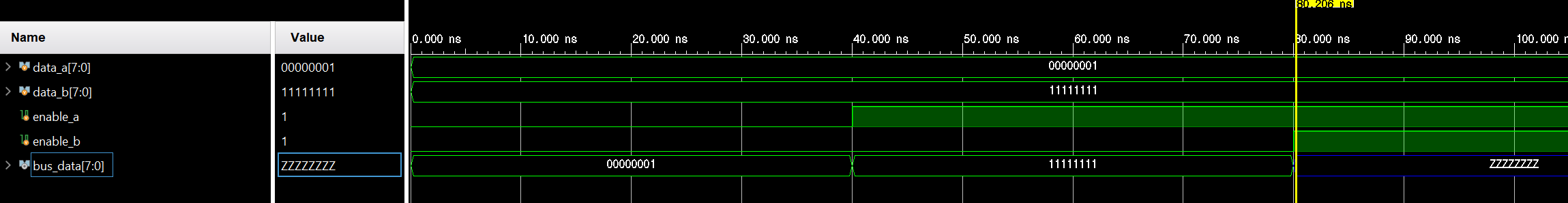

★ 일반적으로, 데이터 버스에는 다수의 신호원들이 연결되므로 버스의 부하 용량이 매우 커지게 되고 따라서 시스템의 동작속도를 저하시키는 주요한 원인 중 하나가 된다. 버스에 대한 부하용량을 감소시키기 위해 다음과 같이 멀티플렉서를 이용하여 신호원을 선택한 후 버스에 연결하는 방식이 사용된다. 그림의 버스 드라이버를 조건 연산자를 사용하여 모델링 하고, 시뮬레이션을 통해 검증한다. enable_a = 1이면 data_a가 버스로 출력되고, enable_b =1이면 data_b가 버스로 출력되며, enable_a와 enable_b가 동시에 1이 되는 경우에는 bus_data를 high-impedance가 된다. 데이터는 8bit으로 설계한다.

// 설계과제 10.9

module multiplexed(data_a,data_b,enable_a,enable_b,bus_data);

input [7:0] data_a, data_b;

input enable_a, enable_b;

output reg [7:0] bus_data;

always@(*)begin

if(enable_a && enable_b) bus_data = 8'bz;

else begin

case(enable_a)

0 : bus_data = data_a;

1 : bus_data = data_b;

default : bus_data = 8'bx;

endcase

end

end

endmodule▣ TESTBENCH

module tb_multiplexed;

reg [7:0] data_a, data_b;

reg enable_a, enable_b;

wire [7:0] bus_data;

multiplexed uo(data_a,data_b,enable_a,enable_b,bus_data);

initial begin

data_a = 8'b00000001; data_b = 8'b11111111;

enable_a = 0; enable_b = 0;

#40 enable_a =1;

#40 enable_b = 1;

#40 $finish;

end

endmodule

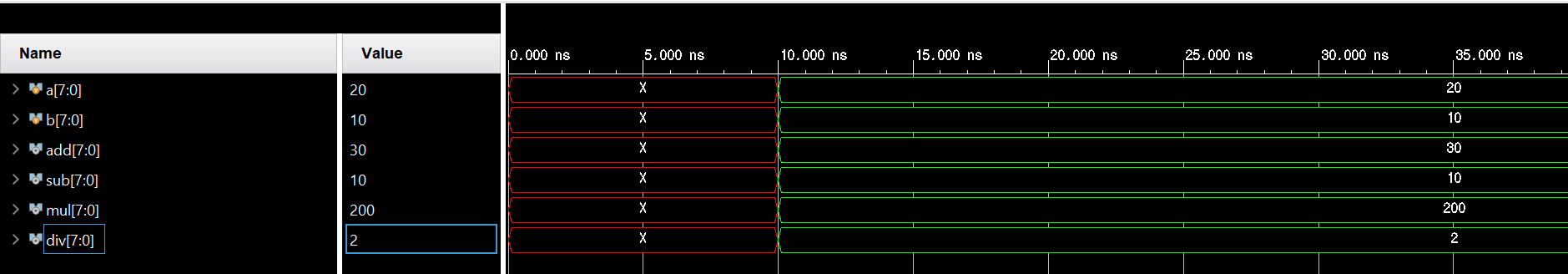

★ 사칙연산에 관한 ALU를 다음과 같이 2가지 방법으로 모델링하고 시뮬레이션을 통해 동작을 확인한다.

① assign 할당문 사용

② always 블록 사용

module combi_test_1(a,b,add,sub,mul,div);

input [7:0] a,b;

output [7:0] add,sub,mul,div;

// 1. assign문 사용

assign add = a + b;

assign sub = a - b;

assign mul = a * b;

assign div = a / b;

// 2. always문 사용

reg [7:0] add, sub, mul, div;

always@(*)begin

add = a + b;

sub = a - b;

mul = a * b;

div = a / b;

end

endmodule▣ TESTBENCH

module tb_combi_test_1;

reg [7:0] a,b;

wire [7:0] add,sub,mul,div;

initial begin

#10 a = 8'd20; b = 8'd10;

#50 $finish;

end

combi_test_1 uo(a,b,add,sub,mul,div);

endmodule

★ 사칙연산에서 overflow가 발생하는 상황을 모델링하고 시뮬레이션을 통해 동작을 확인한다.

더하기, 곱하기 등 사칙연산 연산을 할때 피연산자의 비트 수를 고려해 출려값의 비트 수를 고려해 줘야한다. 항상 연산을 할때는 signed, unsigned타입을 똑같이 맞춰 줘야 한다.

▣ TESTBENCH

module tb_overflow_test;

reg [3:0] a;

reg signed [3:0] b;

reg signed [4:0] correct;

reg signed [4:0] wrong;

initial begin

a = 4'd15;

b = -4'd8;

wrong = a+b;

correct = $signed({1'b0,a}) + b;

end

endmodule

'UVM & RTL > Verilog HDL' 카테고리의 다른 글

| [25] Verilog HDL 순차회로 설계과제 (LATCH, FILP FLOP) (0) | 2022.03.05 |

|---|---|

| [24] Verilog HDL 순차회로 (LATCH, FILP FLOP) (0) | 2022.03.05 |

| [22] Verilog HDL 조합회로 구현 (COMPARATOR, TRI-STATE) (0) | 2022.03.05 |

| [21] Verilog HDL 조합회로 설계과제 (Decoder, Encoder) (1) | 2022.03.05 |

| [20] Verilog HDL 조합회로 구현 (ENCODER, DECODER) (0) | 2022.03.05 |

@Return :: Return

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[25] Verilog HDL 순차회로 설계과제 (LATCH, FILP FLOP)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdyYn1e%2FbtrvcHQlg4U%2FAAAAAAAAAAAAAAAAAAAAAMdB854ggO2aH_jqya5qw9v90ulW-vtr3eTfszio2_0R%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DHroFpzuRuMgwThOjg%252F0rg4yU6%252BY%253D)

![[24] Verilog HDL 순차회로 (LATCH, FILP FLOP)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fb4smZm%2Fbtru2mMBI81%2FAAAAAAAAAAAAAAAAAAAAAHfg_ES7gN_qrF3OZM9OFv5X7h9FoOv5_EXd7IfMWv8C%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DDU3CDhd6iA3MaDhOpHEJvPLMl3c%253D)

![[22] Verilog HDL 조합회로 구현 (COMPARATOR, TRI-STATE)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FGT0FU%2FbtruAsnbZIw%2FAAAAAAAAAAAAAAAAAAAAAAwN8yJsh5q8-SeKXSaODzM6WR5AdHDfIqdJs5X3AGMD%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DUkklgZb1i9oJ%252F3uhYKcFuTeCavk%253D)

![[21] Verilog HDL 조합회로 설계과제 (Decoder, Encoder)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fc7ISVc%2Fbtru8vIRmj8%2FAAAAAAAAAAAAAAAAAAAAAJmcpMXgAiRlIuBBLq0O1ygFRViIVKhWF_wp1-WLXZ1m%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DbQMwaBQ6OjG1IHuJHOSBt5zmHQ8%253D)