![[0] CXL Introduction: why CXL?](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fcc7Zwi%2FbtsHtK9pjrg%2FAAAAAAAAAAAAAAAAAAAAADrprtMExOhLzrbWwqxF6WuRWkUnyzQLPuyuu9yi2hdf%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DWfQqaPr2AqvkGF88zhcxQ275tDI%253D)

CXL(Compute Express Link)는 현재 학계와 산업계에서 큰 주목을 받고 있습니다. 이번 글에서는 CXL에 대한 자세한 기술 설명보다는 현재 데이터 센터에서 발생하는 문제들과 CXL이 이러한 문제들을 어떻게 해결할 수 있는 지에 대해 다루고자 합니다.

왜 CXL이 필요할까?

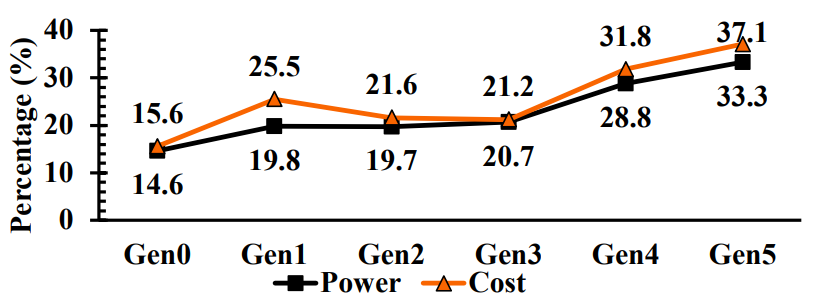

오늘날 data center의 성능을 저해하고, TCO를 증가시키는 중요한 memory 문제들에 직면해 있습니다. Meta에 따르면 전체 TCO중 메모리가 차지하는 비중이 시간이 갈수록 증가하고 있으며 그 수치는 거의 절반에 가깝다고 밝혔습니다. 이러한 문제들은 주로 세 가지 주요 이슈에서 비롯됩니다.

1. DRAM과 SSD간의 지연 시간 차이

첫 번째 문제는 local DRAM과 SSD간의 latency가 차이가 굉장히 크다는 것입니다. local DRAM miss가 발생하면 SSD 스토리지를 이용해야하는데, 이 과정에서 큰 latency가 발생합니다. 이러한 지연은 컴퓨팅 성능에 부정적인 영향을 미칩니다.

2. 프로세서 코어와 메모리 채널의 불균형적인 확장

현대의 멀티코어 프로세서에서는 코어 수가 급격히 증가하고 있지만, main memory channel의 증가 속도는 이를 따라가지 못하고 있습니다. 이 불균형으로 인해 많은 프로세서 코어가 메모리 대역폭 부족에 시달리게 되어, 추가된 코어의 이점을 충분히 활용하지 못하게 됩니다.

3. 가속화 컴퓨팅에서 활용되지 않는 메모리 자원

가속화 컴퓨팅이 증가하면서 가속기가 독립적인 메모리를 가지게 되었지만, 이로 인해 메모리 자원이 충분히 활용되지 않는 문제가 발생하고 있습니다. 이는 사용되지 않는 메모리 자원이 발생하여 비용 증가와 성능 저하를 초래합니다.

이러한 문제들을 해결하기 위해, 프로세서에 더 높은 대역폭과 용량을 유연하게 제공할 수 있는 새로운 메모리 기술이 필요합니다. CXL은 이러한 문제를 해결하기 위해 개발된 산업 표쥰 솔루션으로, 프로세서, 가속기, 메모리 장치 간에 저지연, 메모리 캐시 일관성 링크를 제공합니다.

CXL이 해결하는 주요 문제

1. 시스템 및 장치 메모리에 대한 일관된 접근

전통적으로 시스템 메모리는 DDR 인터페이스를 통해 연결되어 CPU에 의해 cache될 수 있지만, PCIe 장치의 시스템 메모리 접근은 비일관적입니다. 이는 PCIe 장치가 시스템 메모리를 효율적으로 캐시할 수 없다는 것을 의미합니다. CXL은 일관된 메모리 접근을 도입하여 장치가 시스템 메모리를 캐시할 수 있게 합니다.

2. 메모리 확장성

DDR 메모리 인터페이스는 증가하는 메모리 용량과 대역폭 수요를 따라가지 못하고 있습니다. CXL은 PCIe의 높은 핀 당 대역폭을 활용하면서 메모리 일관성을 추가하여 DDR을 대체할 수 있는 적절한 솔루션을 제공합니다. 이를 통해 메모리 대역폭 확장성을 향상시키고, 전통적인 DRAM외의 새로운 메모리 기술을 통합할 수 있습니다.

3. 자원 고립 문제 해결

data center에서 메모리와 같은 자원이 고립되어, 일부 서버는 메모리를 충분히 사용하지 못하고 다른 서버는 메모리가 부족한 상황이 발생합니다. CXL 2.0부터는 여러 host간 리소스 풀링을 도입하여, 재부팅 없이 자원을 동적으로 재할당함으로써 자원 활용을 최적화하고 비용을 절감합니다.

CXL은 데이터 센터의 중요한 메모리 문제를 해결하여 성능, 확장성 및 자원 효율성을 향상시킵니다. 일관된 메모리 접근, 확장 가능한 메모리 대역폭 및 동적 자원 풀링을 제공함으로써, CXL은 현대 컴퓨팅 환경의 진화하는 요구를 지원하며, 더 효율적이고 강력한 데이터 센터의 길을 열어줍니다. CXL이 산업에 널리 채택됨에 따라 데이터 센터 운영이 크게 개선되고, 더욱 복잡한 워크로드를 처리할 수 있게 될 것입니다.

Reference)

- Rambus "Compute Express Link (CXL): All you need to know"

- Maruf, Hasan Al, et al. "TPP: Transparent page placement for CXL-enabled tiered memory." Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 3. 2023.

- Li, Huaicheng, et al. "Pond: Cxl based memory pooling systems for cloud platforms." Proceedings of the 28th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, Volume 2. 2023.

- Sharma, Debendra Das, Robert Blankenship, and Daniel S. Berger. "An introduction to the compute express link (cxl) interconnect." arXiv preprint arXiv:2306.11227 (2023).

'Interface Standards > CXL' 카테고리의 다른 글

| [5] CXL - Transaction layer - Transaction Flow (0) | 2024.07.07 |

|---|---|

| [4] CXL - Transaction layer - CXL.mem protocol (0) | 2024.07.07 |

| [3] CXL - Transaction layer - CXL.cache protocol (0) | 2024.07.07 |

| [2] CXL - Transaction layer - CXL.io protocol (0) | 2024.07.07 |

| [1] CXL Architecture (0) | 2024.07.07 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[4] CXL - Transaction layer - CXL.mem protocol](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbsQ6ml%2FbtsIqys09SN%2FAAAAAAAAAAAAAAAAAAAAAAdextjXv4mWig7ZRU1U42p_tllgGs8dIdHqiVMcVkuc%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3Dde%252FVA0hiyQWQcQz4fn8TYPXFq3M%253D)

![[3] CXL - Transaction layer - CXL.cache protocol](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FljwLu%2FbtsIpMetjzO%2FAAAAAAAAAAAAAAAAAAAAACkzXpyv0k7Kn79HKrFqd0UdXH4ch39mUeIIoLQs9cuu%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DkyafUGlPJiPWU3yyXn%252B1Ai2kp8I%253D)

![[2] CXL - Transaction layer - CXL.io protocol](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FetpnR3%2FbtsIpukUvYj%2FAAAAAAAAAAAAAAAAAAAAAMlPnKHuEje_TL1jdCXVty2YHIoZyjCYN0nrxS2WKIYu%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3D1Quy7EcTI8QxBIM9jJ4xPYBV58U%253D)

![[1] CXL Architecture](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FxCyfl%2FbtsIo7XJPFN%2FAAAAAAAAAAAAAAAAAAAAAGnHTwmrV36qRlmNsveY7tn4WOvNBaz-sZc0eWVydR6g%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DaEJv1%252BUyWWWb2qxuA%252FcL02oBKzI%253D)