![[2] PCIe - Transaction Layer (TLPs)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbQy5kg%2FbtsHn4Mu5EI%2FAAAAAAAAAAAAAAAAAAAAAPXNnRGkawUXPeWzeNLZ1HejVn25h9YOlhAF2wzR9053%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DaBXN%252B%252BPZpCpaOQCPtQ55ruu6stw%253D)

이 글은 제가 PCIe를 공부하면서 겪은 시행착오를 바탕으로 정리한 글입니다. PCIe를 처음 접하는 분들에게 좋은 길라잡이가 되었으면 합니다.

이전 글)

[1] PCIe - Introduction 2

returnclass.tistory.com

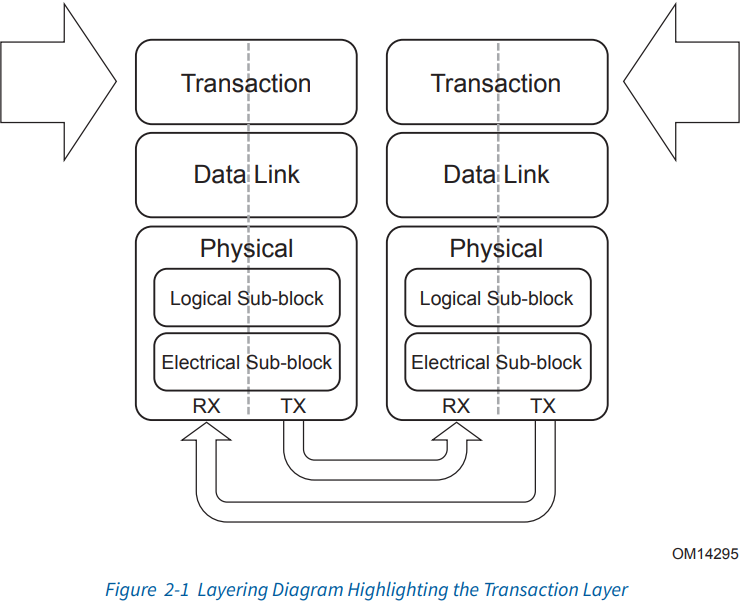

Transaction Layer 소개

PCIe의 transaction layer는 CPU 혹은 device core로부터의 memory read/write, I/O configuration, message 요청을 받아 처리합니다. 이 계층에서는 요청의 성격에 맞게 Transaction Layer Packets(TLPs)를 형성하고, 이를 통해 목적지 주소와 라우팅 정보를 포함시켜 패킷을 구성합니다. 또한 데이터의 무결성을 보장하기 위해 선택적으로 CRC를 추가하고, 완성된 TLP는 data link layer로 전송되어 device 간의 통신을 준비합니다.

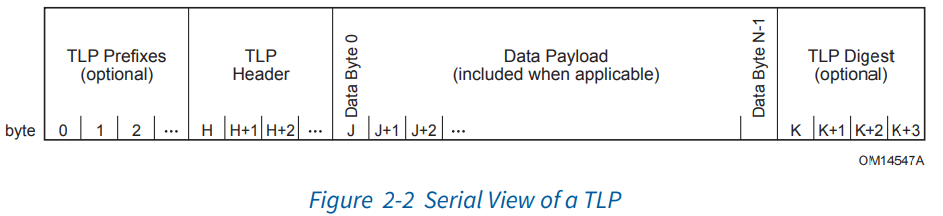

TLP Header

TLP는 데이터 전송을 위한 기본 단위입니다. TLP는 주로 데이터와 관련 명령을 전송하는 데 사용되며, 밑의 그림과 같이 모든 TLP는 TLP header를 포함하고 있습니다. TLP header에는 packet의 유형, 크기 그리고 목적지 등 중요한 접보를 담고 있어 packet이 올바르게 전송되고 처리될 수 있도록 도와줍니다.

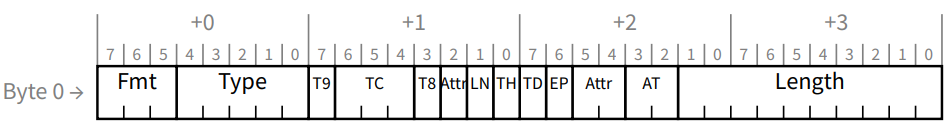

Common Packet Header Fields

TLP의 구조는 transaction 유형에 따라 달라질 수 있으나 먼저 공통적으로 동일한 부분부터 알아보도록 합시다.

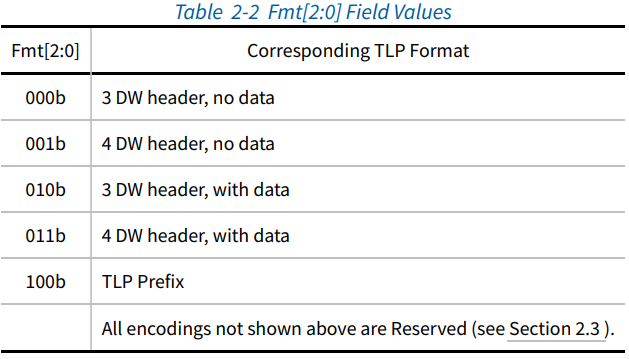

Fmt(Format)

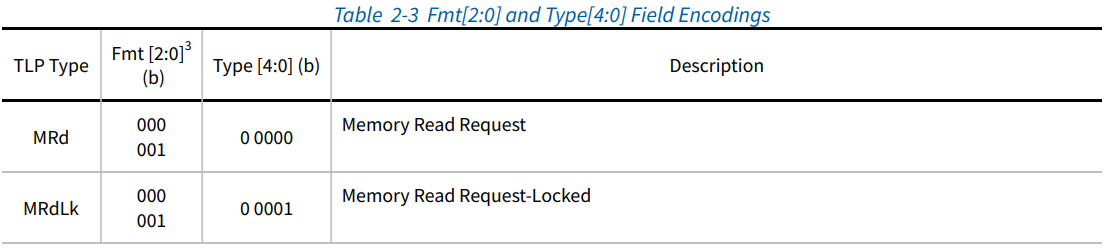

Fmt 필드는 TLP의 기본 형식을 지정하며, 주로 패킷이 데이터를 포함하는지 여부와 패킷의 크기 및 구조를 나타냅니다. fmt 필드는 일반적으로 3bit로 구성되며 다음 표와 같은 정보를 포함할 수 있습니다.

Type

Type 필드는 TLP의 종류를 구체적으로 지정하며, 어떤 종류의 작업을 수행하는지를 나타냅니다. 5bit으로 구성되며, 각 비트 조합은 다양한 transaction 유형을 나타냅니다. 다음 예시는 2개의 정보만 담고 있으며, Fmt필드의 정보가 2개씩 있는 이유는 32bit address와 64bit address 정보를 구분하기 위함입니다. 추가적인 type 필드의 정보는 PCI Express® Base Specification을 참고해 주세요.

Tag

Tag 필드는 특정 TLP를 고유하게 식별하고 관리하는 데 사용되는 구성 요소입니다. 이 필드는 주로 다수의 동시 transaction을 처리하는 과정에서 각각의 TLP를 구분하는데 사용되며, tag 필드의 T9, T8로 표시된 Tag 부분은 PCIe 세대가 증가하면서 필요에 의해 추가된 tag의 확장 bit입니다. non-posted의 경우 outstanding request에 대한 식별자로 사용됩니다.

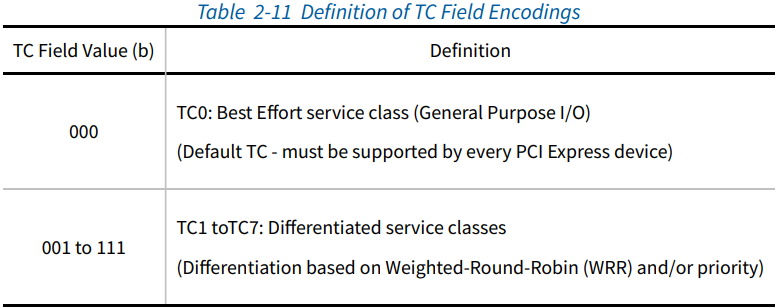

TC(Traffic Class)

TC필드는 패킷이 속하는 traffic class를 정의합니다. 이는 패킷의 우선 순위 및 QoS를 결정하는 데 사용됩니다. 네트워크에서 데이터 트래픽을 구분하고 관리하기 위해 사용되는데, 다양한 traffic class는 네트워크 리소스가 경합될 때 우선순위를 결정하는 데 중요한 역할을 합니다. TC0이 우선순위가 제일 낮으며, TC7이 가장 높다.

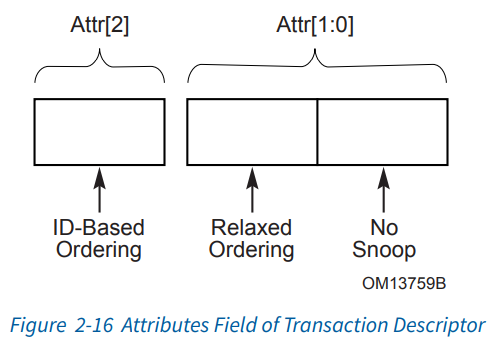

Attr(Attributes)

Attributes 필드는 transaction의 특정 속성을 지정하는 데 사용되며, 이는 데이터 처리 방식에 영향을 줍니다. 먼저 떨어진 bit인 Attr[2]는 ID-based ordering 여부를 나타냅니다. 1이면 동일한 ID를 가진 TLP들은 순서대로 처리가 되도록 합니다. 이는 데이터 일관성 및 순차적 처리가 중요할 때 활성화됩니다.

Relaxed ordering 속성이 활성화되면, 데이터 패킷은 엄격한 순서대로 처리될 필요가 없습니다. 즉, 시스템은 데이터 처리의 효율성을 높이기 위해 입력된 순서와 다르게 패킷을 처리할 수 있습니다. 이는 리소스에 대한 지연 시간을 줄이고 전체적인 시스템 성능 향상시키는 데 도움을 줍니다.

No Snoop 속성이 활성화되면, 해당 패킷은 캐시 일관성 메커니즘(MESI)의 대상이 되지 않습니다. 즉, 시스템은 이 데이터 패킷을 처리할 때 캐시 메모리의 상태를 검사하거나 업데이트하지 않습니다. 이 설정은 주로 캐시가 필요 없거나 캐시 일관성이 유지될 필요가 없는 데이터 전송에 사용됩니다.

LN(Lightweight Notificiation)

일종의 cache coherency 관련 bit입니다. 특정 cache line의 업데이트가 발생했을 때 endpoint에 하드웨어 메커니즘을 통해 알림을 제공합니다.

TH(TLP Processing Hint Field)

TH 필드는 transaction과 관련된 data를 어떻게 처리할지를 결정하는 데 도움을 주기 위한 정보를 제공합니다.

- 00: device 및 host 양쪽에서 자주 읽히고 쓰여지는 경우. cache에 유지하기 적합

- 01: device가 자주 읽고 쓰는 경우에 사용. device cache에 caching 하기 적합

- 10: 한쪽에서는 data를 쓰고 다른 쪽에서는 data를 읽는 경우. cache 정책에 맞춰 조정

- 11: 10과 유사하지만, 높은 temporal locality를 가지고 자주 재사용될 것으로 예상되는 경우, 이 data를 우선적으로 caching

TD(TLP Digest Field)

TLP의 ECRC 유무를 나타내는 필드입니다. data link layer에서 생성하는 LCRC는 필수지만, transaction layer에서 발생하는 ECRC는 선택이기 때문입니다. (참고로 ECRC는 data payload에 대한 CRC가 아닌 TLP header(prefix가 있다면 prefix까지)를 바탕으로 생성됩니다.)

EP(Poisoned TLP Data)

1bit 필드로 1이면 TLP data가 손상되어 있다는 의미입니다. 이는 error forwarding과 관련이 있는데 손상된 데이터를 수신 측에 전달하여 오류가 발생함을 알리며, 적절한 조치를 취할 수 있도록 합니다. 수신 측은 필요에 따라 오염된 데이터를 사용하거나 버릴 수 있습니다. 참고로 EP bit가 전송 중에 변할 수 있기 때문에 수신 측에서 ECRC check를 할 때 EP bit의 값은 1 값으로 가정합니다.

AT(Address Type)

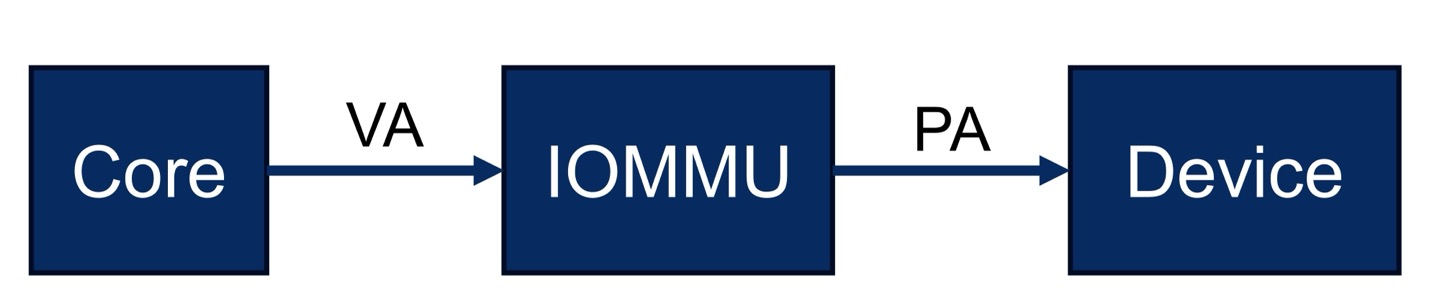

Address type 필드는 주소 전송시 사용되는 주소 유형을 지정합니다. 일반적으로 2bit으로 구성되며, 00일 경우 특별한 주소 변환 없이 memory request가 진행되며, 01일 경우 주소 변환 요청이 필요하다는 것입니다. virtual address를 phyiscal address로 변환해야 하는 경우가 이에 해당합니다. 10 값은 주소가 이미 변환되었음을 나타냅니다.

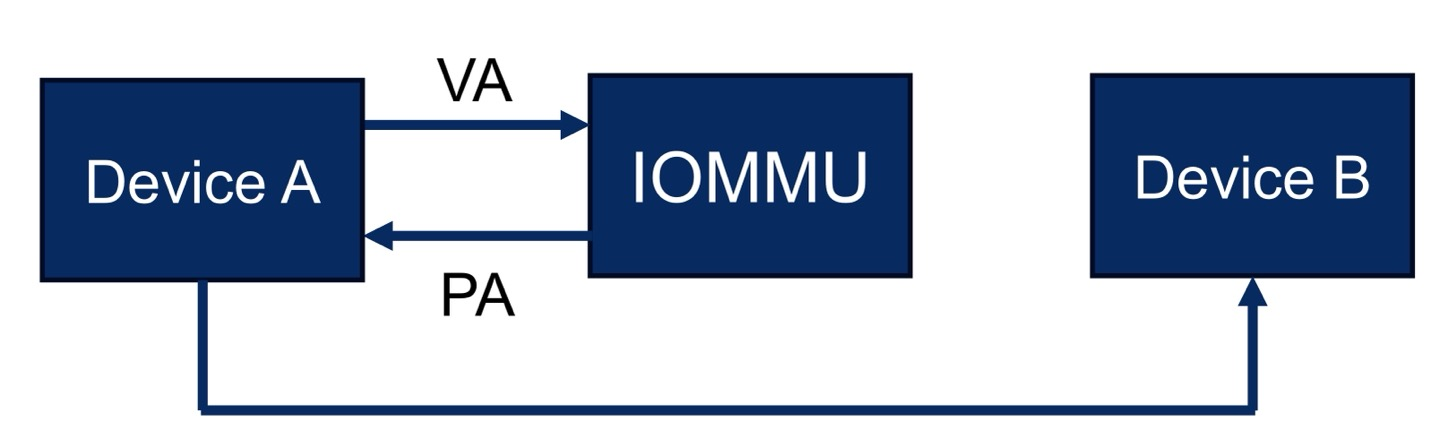

참고) ATS(Address Translation Service)

일단 기본적으로 집고 넘어가야 되는 부분은 PCIe bus를 physical address로 움직인다는 것입니다. 예를 들어, Host CPU/Core가 PCIe device에 접근할 때는 왼쪽 그림과 같이 실행될 것입니다. 이 과정은 ATS와 무관합니다. 하지만 Device Core가 Host CPU/Core 또는 다른 PCIe device에 접근한다고 가정해 봅시다. device core A가 VA를 통해 device B에 접근하는데, PCIe bus는 PA이기 때문에, address translation이 필요합니다. 즉, PTE를 얻기 위해 page table에 접근해야 하는데 이때 ATS가 사용됩니다. device A가 page table에 접근하는 것이 아닌 IOMMU에 ATS request를 보내면, IOMMU가 ATS response로 변환된 주소와 permission을 줍니다.

Length

전송할 data의 길이를 DW로 지정한 값입니다. 1DW(4B) 부터 1024DW(4096B)까지 지정할 수 있으며, 시작 주소에서 길이를 더한 값이 4KB boundary를 넘어가서는 안됩니다.

Specific Packet Header Fields - Memory, Completion, Configuration, IO

Memory Request

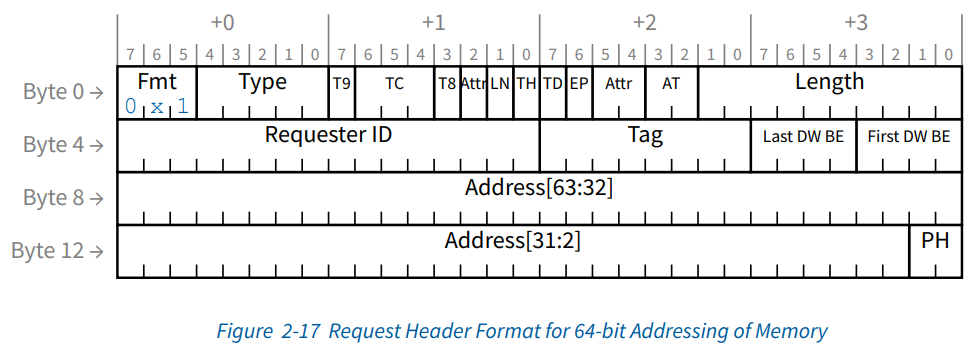

64bit address일 경우는 TLP header의 크기는 4DW이며, 32bit address일 경우 3DW입니다. 이는 Fmt 필드에서 확인할 수 있습니다. 다음 예시는 64bit address를 사용하는 memory request에 대한 TLP header입니다.

Requester ID 필드

이 필드는 memory read의 경우 requester로 올 completion TLP에 대한 일종의 return address라고 생각하시면 됩니다. 다만 memory write인 경우 completion이 따로 필요하지 않지만 다른 용도로 이 공간이 활용됩니다(e.g., error reporting).

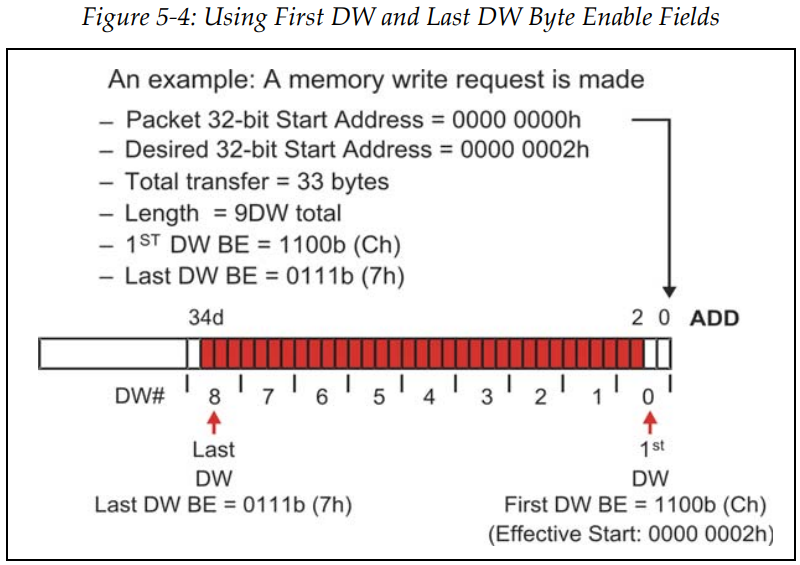

Byte Enable(BE) 필드

이 필드는 transaction 중 특정 데이터 바이트가 유효한지를 나타내는 요소입니다. 이는 데이터 패킷의 특정 부분만을 대상으로 작업을 수행할 때 중요합니다.

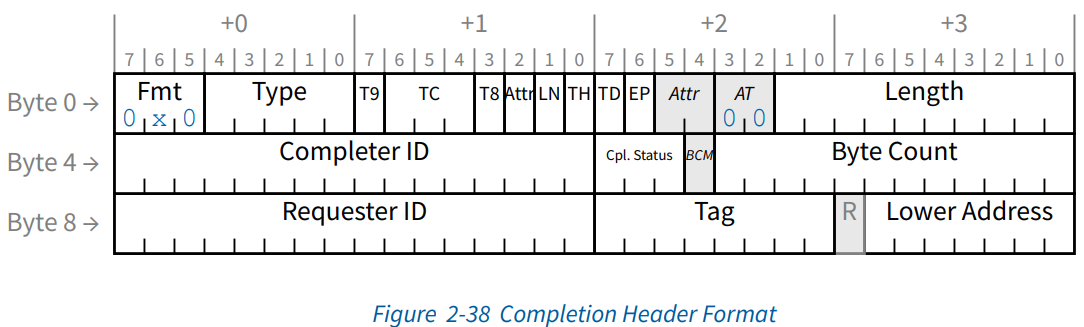

Completions

Memory read가 성공적일 경우, 요청된 data와 함께 completion이 반환됩니다. 이 header 구조의 특징으로는 3DW 크기의 header를 사용하며, completion은 requester ID를 기반으로 routing 됩니다. 이 ID는 원래 요청을 보낸 장치를 식별하여, 해당 장치로 정확한 완료 메시지를 전송하기 위해 사용됩니다. 또한 요청에서 받은 일부 필드의 경우 변경 없이 completion에 그대로 반환됩니다. 또한 tag를 통해 requester가 보낸 여러 요청 중에 정확히 어떤 요청이 완료되었는지 식별할 수 있게 도와줍니다.

Completer ID 필드는 completer의 BDF정보를 가지며, 일반적인 상황에서는 사용하지 않지만, 오류가 있는 경우 일종의 return address 정보로 사용합니다.

Completion Status Code 필드

말 그대로 completion의 상태를 나타냅니다. 예를 들어, 000의 경우 successful completion을 의미하며, 다른 값들은 어떠한 문제가 생겼다는 의미를 가집니다. 이는 반환된 data와 상관없이 transaction이 실패함을 의미합니다.

Byte Count 필드

이 필드는 전송 중 남은 data의 수를 나타내는 필드입니다. 예를 들어 총 전송 데이터의 양이 100바이트인데 한 번에 전송할 수 있는 최대 전송양이 60바이트라면 한 번 전송한 후의 byte count필드는 40이라는 값을 띄고 있을 것입니다.

참고) BCM과 Lower Address는 과거 PCI-X에서 사용되는 필드이므로 스킵하겠습니다.

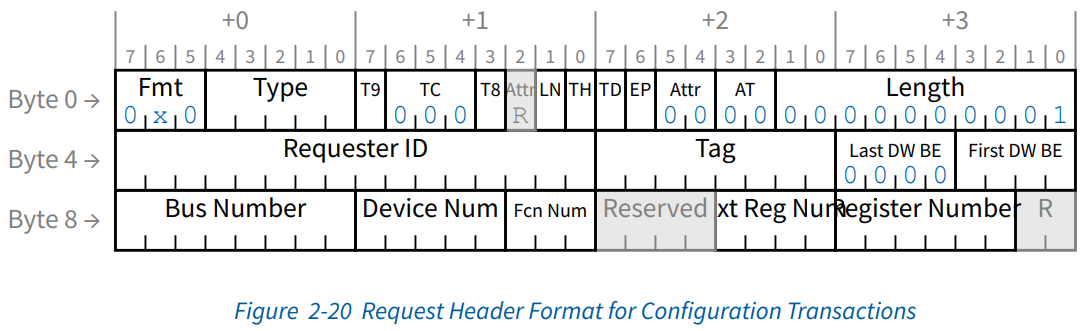

Configuration

configuration request에 관련된 TLP header 정보입니다. Byte 8의 Bus/Device/Function 번호가 target BDF를 가리키며, Register Number는 target config register를 가리킵니다.

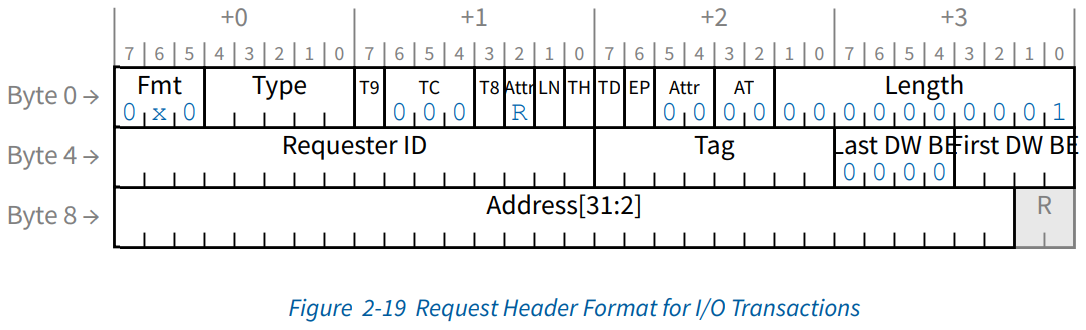

IO

IO request에 사용되는 TLP header 정보입니다.

Next Topic)

이번 글을 통해서 TLP 및 TLP header를 자세하게 알아보았습니다. 다음 글에서는 transaction layer에서 하는 역할들을 위주로 알아봅시다.

Reference)

- PCI Express® Base Specification Revision 5.0 Version 1.0

- PCI Express Technology 3.0 (minshare)

'Interface Standards > PCIe' 카테고리의 다른 글

| [5] PCIe - Data Link Layer (DLLP & Ack/Nak protocol) (0) | 2024.05.13 |

|---|---|

| [4] PCIe - Transaction Layer (Ordering) (0) | 2024.05.12 |

| [3] PCIe - Transaction Layer (Quality of Service & Flow Control) (0) | 2024.05.12 |

| [1] PCIe - Introduction 2 (0) | 2024.05.11 |

| [0] PCIe - Introduction 1 (0) | 2024.05.11 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[4] PCIe - Transaction Layer (Ordering)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fdu0fWN%2FbtsHnkCGf50%2FAAAAAAAAAAAAAAAAAAAAAF2GvYVLDYR8YAdeMEN9E8d9Y-qw3y3itS7P-eifwgNA%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3Drp33k5S2CacQRP%252FeEgNjsnP2HkI%253D)

![[3] PCIe - Transaction Layer (Quality of Service & Flow Control)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FJJ6A7%2FbtsHnwioodF%2FAAAAAAAAAAAAAAAAAAAAAFyOMpJpr78qdb31lq1CaPyH2msBJAQeuezhRcY6eRUG%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DQHWUOty9VLDpdfnRbPdXdN3N4jI%253D)

![[1] PCIe - Introduction 2](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbvLHal%2FbtsHnTYAKKB%2FAAAAAAAAAAAAAAAAAAAAAM1_jlR2BqX3JfvfiT0qH9vD0dFbMzSNd0cNGP4LbQhB%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DQczFWNL72TmdxOysGPiM3OTZJwI%253D)

![[0] PCIe - Introduction 1](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbRCdmA%2FbtsHnG59zla%2FAAAAAAAAAAAAAAAAAAAAABzBySjCH8PHtC_PvcZ4Sse7cMUzpppDbt5frNDbDxaE%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DkY%252BKiNe08GYJ7sIGcjm%252BzYq%252FLP4%253D)