![[6] CXL - Link layer - Flit Packing](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcVRtA5%2FbtsJmoJ6RS3%2FAAAAAAAAAAAAAAAAAAAAALa-799BdoO1mXoYEDxJDwZGljfu_Nj8hzoJZxDkxBEc%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3D4OuJqk3s8DW5SRMm7pzM3U0H9is%253D)

이전글)

[5] CXL - Transaction layer - Transaction Flow

CXL spec이 매우 방대한 내용을 담고 있기 때문에 본 블로그에서는 CXL spec을 이해하기 위해 도움이 될 만한 것들을 골라서 간략히 정리하였습니다. 자세한 내용은 PCIe/CXL spec을 참고해주세요. 이전

returnclass.tistory.com

Link Layer 소개

CXL에서 Link Layer는 흔히 CXL 코어라고도 불리며, 두 가지 주요 역할을 담당합니다. 첫 번째는 CXL에서 데이터 이동의 기본 단위인 flit을 패킹하고 언패킹하는 것이고, 두 번째는 CRC 생성을 통해 데이터의 무결성을 확인하며, 필요시 retry 메커니즘을 실행하는 것입니다. 이 retry 방식은 PCIe의 ack/nak 프로토콜을 기반으로 한 방식과 매우 유사합니다. 주요 차이점은 PCIe의 경우 ack/nak 신호를 전송할 때 TLP가 아닌 전용 DLLP를 사용하지만, CXL에서는 flit에 ack 필드를 포함시켜 CXL 장치 간에 flit을 주고받을 때 자연스럽게 ack 전송이 가능하다는 점입니다.

Flit Packing

이번 장에서는 flit이 어떻게 packing되는지에 중점을 두어 설명하겠습니다. flit을 unpacking하는 동작은 packing의 역순이라고 생각하시면 됩니다. CXL에서 flit은 크게 세 가지 종류로 나눌 수 있을 것 같습니다. 첫번째는 가장 일반적인 flit 유형인 protocol flit, 두 번째는 flit의 모든 slot이 data로만 구성되어 있는 all data flit, 마지막으로 특정 상황에 사용되는 control flit입니다. flit을 구분할 때 흥미로운 점이 하나 있는데, protocol flit과 control flit을 구분하는 1bit field는 있지만 이상하게도 all data flit을 구분하는 field는 있지 않습니다. 즉, all data flit은 protocol flit과 동일한 flit으로 취급되지만 특정 상황에 의도적으로 나오게끔 설계되어야 합니다. (뒤에서 rollover와 관련되서 설명하겠습니다.)

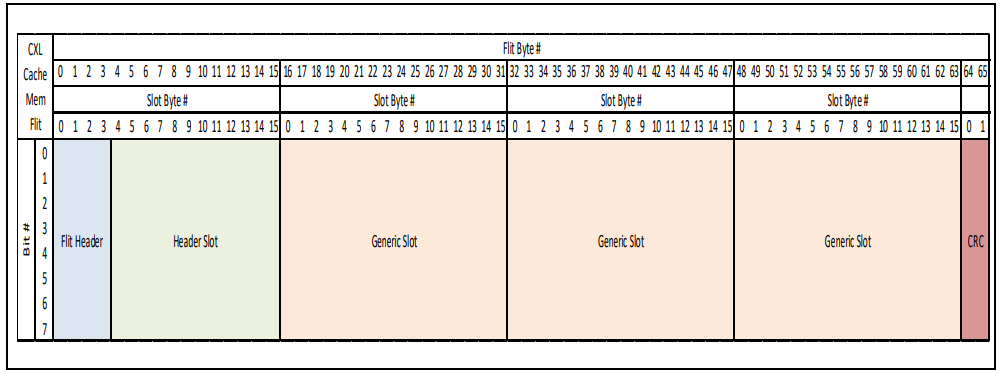

앞서 말한 3가지 flit은 모두 flit header(optional) slot 4개 + CRC로 구성되어 있으며, link layer에서 최종적으로 생성되는 flit의 크기는 66byte입니다. 흔히 CXL에서 flit의 크기는 68byte (CXL3.0에서는 256B도 지원합니다.) 라고 알려져 있습니다. 여기서 중요한 점은 CXL link layer에서는 66byte 크기의 flit이 만들어지면 나머지 2byte는 physical layer에서 생성된다는 점입니다.

slot에는 여러가지 유형으로 나누어져 있습니다. 먼저 protocol flit의 경우에는 slot 0에는 Header slot을 사용해야되며, 나머지 slot 1~3까지는 general slot을 사용해야합니다. header slot과 general slot에도 여러가지 유형들로 나누어져 있으며, 각 유형별로 담을 수 있는 메세지가 다릅니다. 즉, 주어진 input에 따라 packing 알고리즘은 어떤 타입의 slot을 사용해야될지 결정해야합니다. 이러한 관점에서 최적화와 관련된 성능 차이가 크게 나타나며, CXL에서 packing 알고리즘이 중요한 이유 중 하나입니다. (일례로 intel에 발간한 CXL 소개 자료 중, futre work 중 하나가 더 나은 packing 알고리즘입니다.) 각 slot이 어떻게 구성되는지는 본 글에서 다루지 않을 예정이며, 자세한 사항은 스펙에서 쉽게 확인할 수 있을 것입니다.

Flit Packing Rule

CXL 스펙에서는 flit이 만들어질때 일종의 packing rule을 명시하고 있습니다. 이번 글에서는 CXL 스펙에서 제시하는 모든 packing rule은 살펴보지 않을 것이며, 대표적인 몇 가지 케이스만 살펴봅시다. (자세한 packing rule은 CXL 스펙을 참고해주세요.)

위 그림은 CXL 스펙에서 제시하고 있는 protocol flit의 예시를 나타내고 있습니다. 이 예시에서 몇 가지 rule을 살펴보면, 첫 번째로 Data Header를 포함하는 slot(예제 그림에서는 slot 2(G2))이 올 경우, 그 다음 slot은 무조건 16B data를 담고 있는 G0 slot이 와야합니다. 그래서 slot 3의 유형이 G0인 것을 볼 수 있습니다. 그리고 그 다음 보낼 flit에 전달하지 못한 data를 우선적으로 전달해야합니다. 즉, 다음 flit의 slot 1~3에 48B data(64B cache line을 기준으로 함)를 추가적으로 전송해야합니다. slot 0는 무조건 header type의 flit이 오기때문에 slot 1~3에 data를 담아야합니다. 만약에 추가적으로 전송해야하는 data가 64B이상이여서 G0 slot이 4개 이상 필요할때는 protocol flit이 아닌 all-data flit이 필연적으로 나와야합니다. 이렇게 하나의 flit에 전송하고 남은 data slot을 rollover라고 보통 표현을 합니다.

또 다른 packing rule은 valid한 slot들 사이에 invalid한 slot이 포함되면 안됩니다. 위 예시에서는 모든 slot들이 valid한 채로 꽉꽉 담겨 있기 때문에 packing rule에 어긋나지는 않지만, 만약 slot 1이 invalid했다면, 이 flit은 flit packing rule에 위반될 것입니다.

다음 글에서는 CXL link layer의 또다른 주요 기능인 retry 메커니즘에 대해 간략히 소개하는 시간을 갖도록 하겠습니다.

Reference)

- Compute Express Link Specification

'Interface Standards > CXL' 카테고리의 다른 글

| [8] CXL - ARB/MUX Layer (0) | 2024.08.30 |

|---|---|

| [7] CXL - Link layer - Retry (0) | 2024.08.30 |

| [5] CXL - Transaction layer - Transaction Flow (0) | 2024.07.07 |

| [4] CXL - Transaction layer - CXL.mem protocol (0) | 2024.07.07 |

| [3] CXL - Transaction layer - CXL.cache protocol (0) | 2024.07.07 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[8] CXL - ARB/MUX Layer](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdpzeEF%2FbtsJmOuSPz7%2FAAAAAAAAAAAAAAAAAAAAACSqDlSSvbyftPcsEqqTILTgTRV7eLD_kW_QmAkZSw1t%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DF%252FQO4oNyA8niAoByA0IYfroLtiY%253D)

![[7] CXL - Link layer - Retry](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fceev4K%2FbtsJnvIdO8U%2FAAAAAAAAAAAAAAAAAAAAAA-Xc2dPuspgAPK3MOrbOWtqysOf2pcQS6KXw8kaoH0H%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DaBL4hOWbMedyardn48LrUHe4dEs%253D)

![[5] CXL - Transaction layer - Transaction Flow](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fc9DVhI%2FbtsIqEz16DZ%2FAAAAAAAAAAAAAAAAAAAAAHlIvfktm_wGI2rxs5vRsd8vPX9xmGb8Axyq8qBAyc8f%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3Ds0%252BH0Z9RKMbrpDaWMJrel3wrHXU%253D)

![[4] CXL - Transaction layer - CXL.mem protocol](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbsQ6ml%2FbtsIqys09SN%2FAAAAAAAAAAAAAAAAAAAAAAdextjXv4mWig7ZRU1U42p_tllgGs8dIdHqiVMcVkuc%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3Dde%252FVA0hiyQWQcQz4fn8TYPXFq3M%253D)