![[9] CH7 조합논리회로 < 3상태 버퍼 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdyPpKZ%2FbtrpPFSbhj1%2FAAAAAAAAAAAAAAAAAAAAAGi7ROiTjqdLrOoy6Yo1BnyOhugdPmeVkLS4phUDTcxe%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3Dt%252BgY12SevU9Mdl8vEhAjnC5ykwo%253D)

[9] CH7 조합논리회로 < 3상태 버퍼 >Computer Architecture/논리회로2022. 1. 5. 14:07

Table of Contents

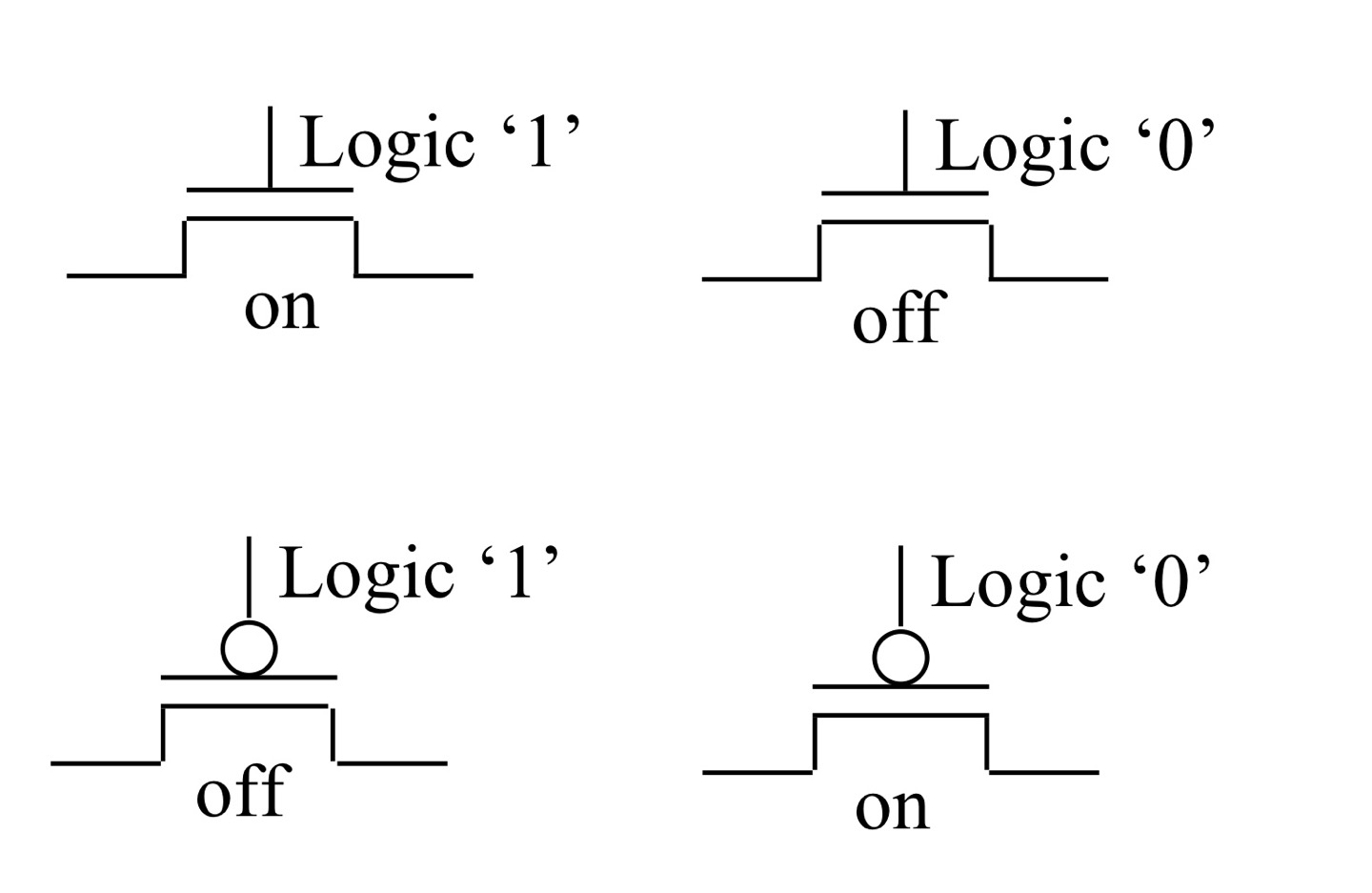

< NMOS Transistor >

- Logic 1을 gate에 가하면 on

- Logic 0을 gate에 가하면 off

< PMOS Transistor >

- Logic 1을 gate에 가하면 off

- Logic 0을 gate에 가하면 on

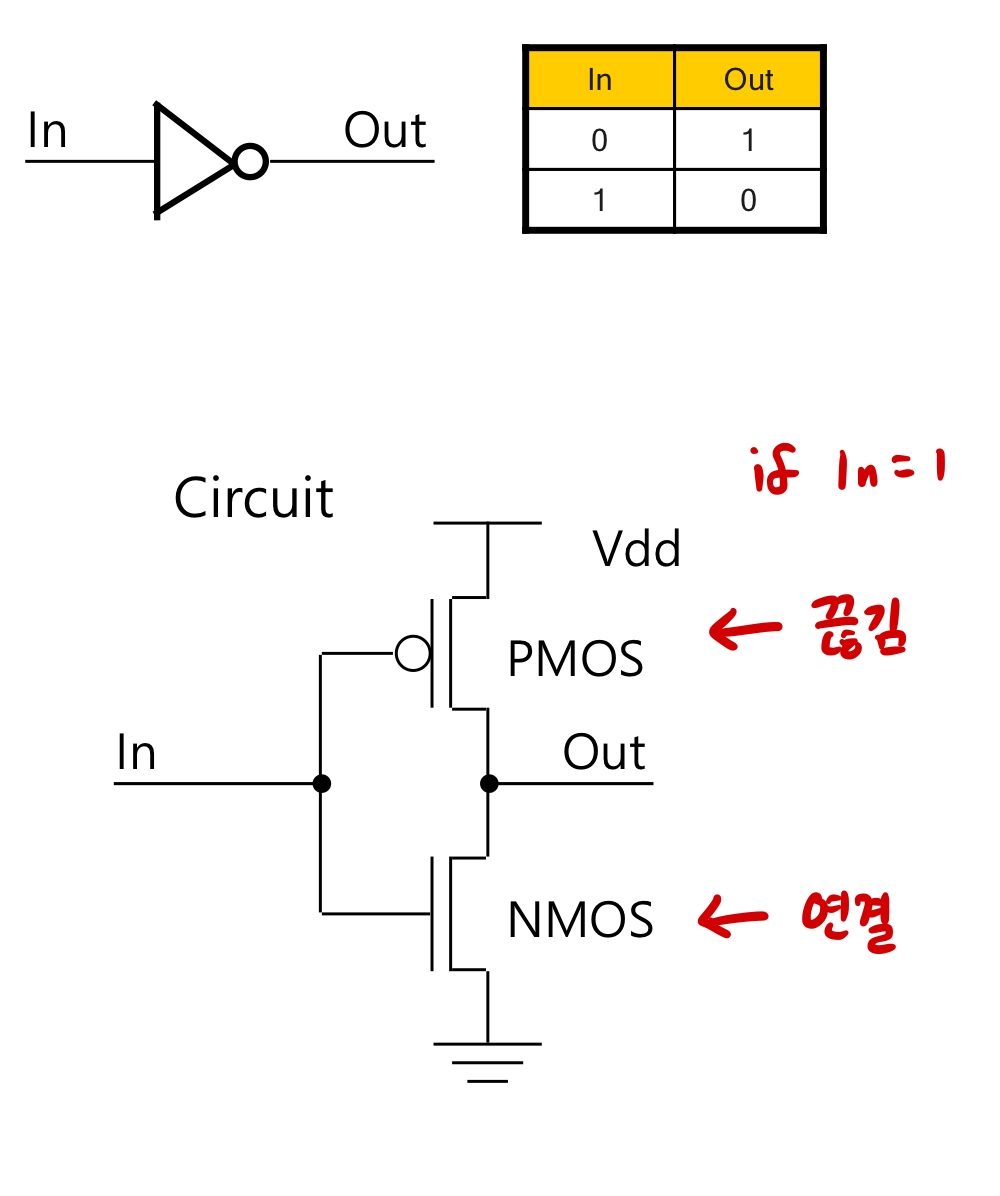

< CMOS 인버터 >

< Inverter Operation >

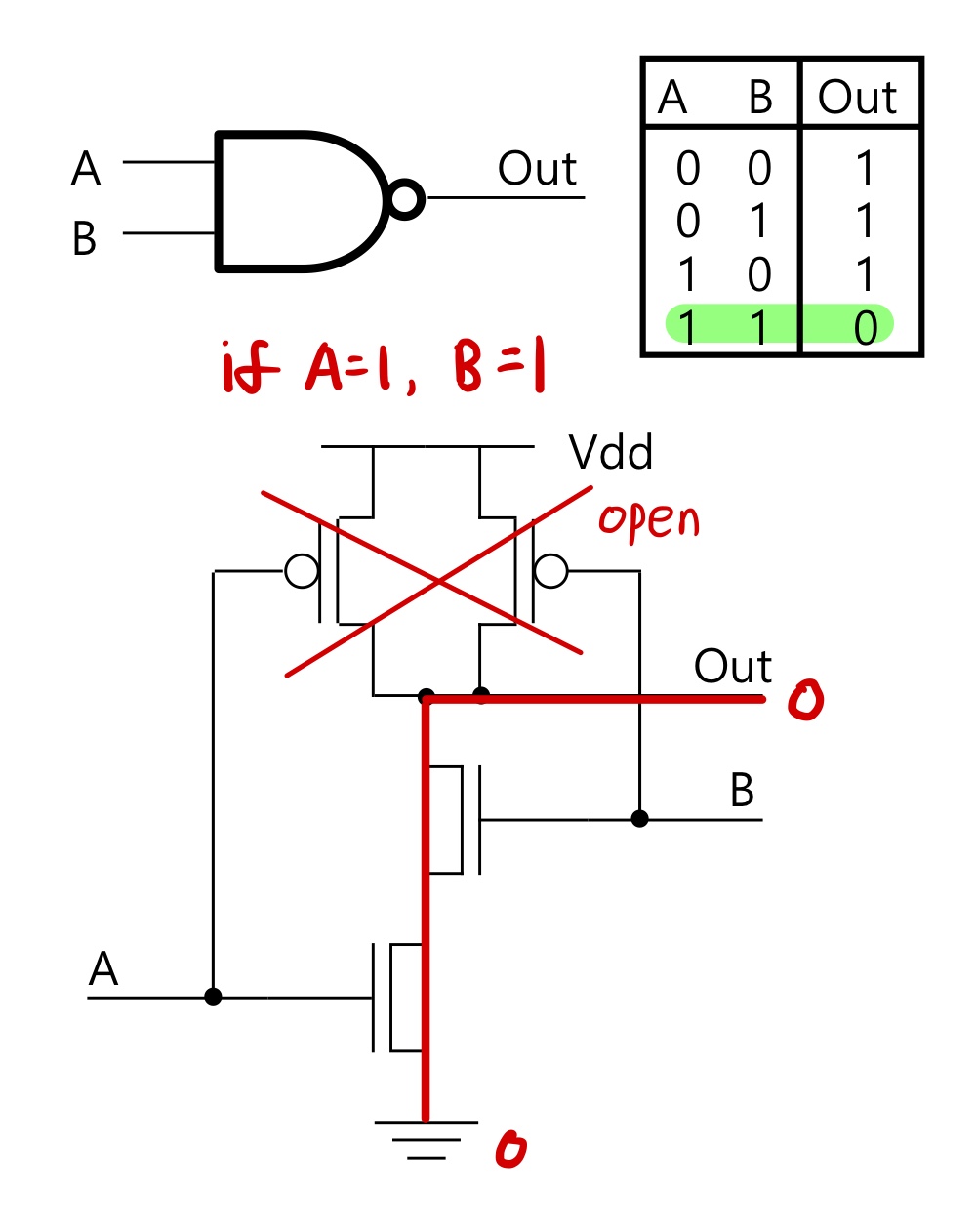

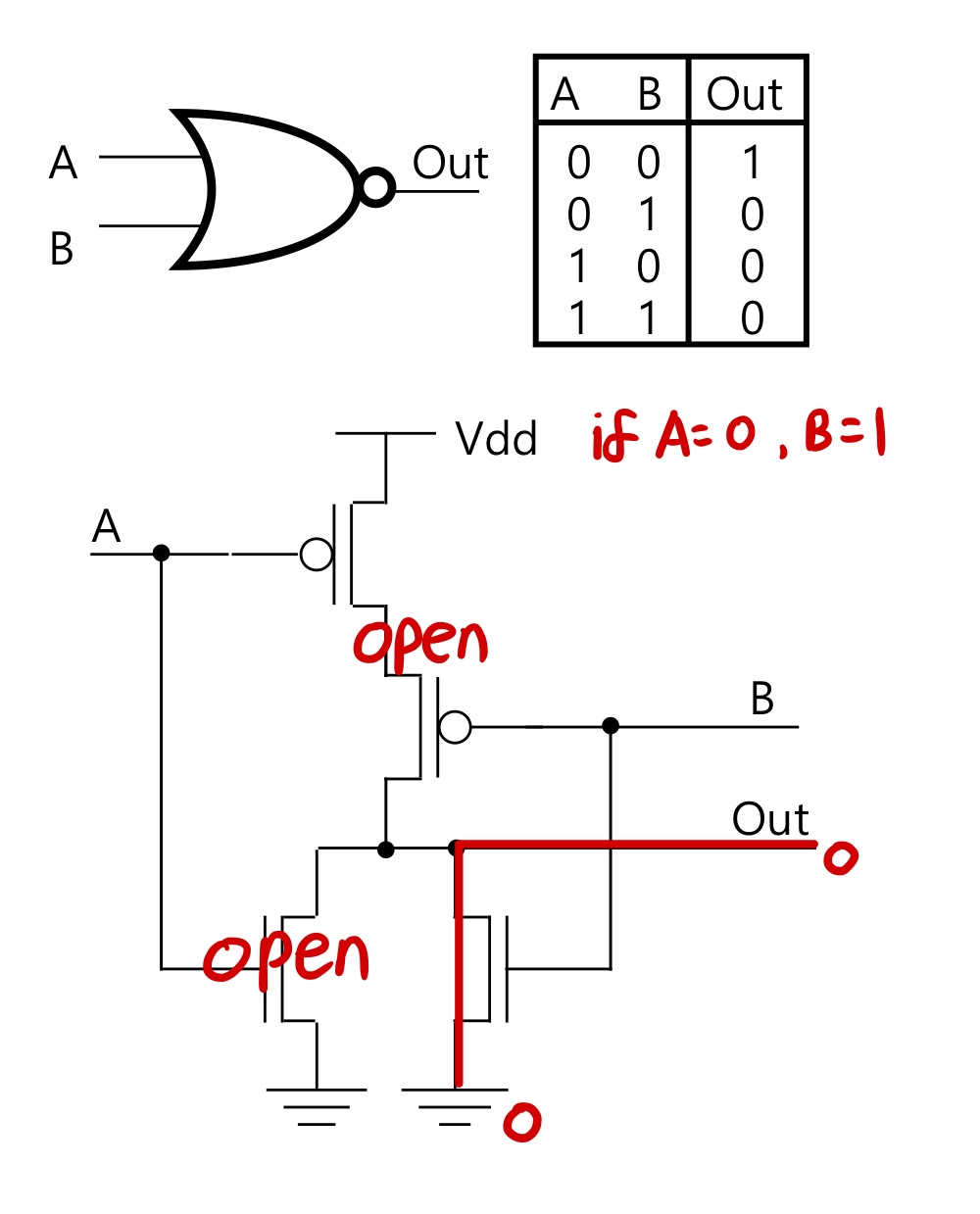

< CMOS NAND , NOR게이트 >

< 복합 게이트 >

출력 OUT가 1이 되기 위해서는

- D'*(A'+(B'*C')) : D는 무조건 연결되야 하고, A 혹은 B,C가 연결되어야 합니다.

- (D+A*(B+C)' : D가 끊어지거나, A또는B가 끊어져야 합니다.

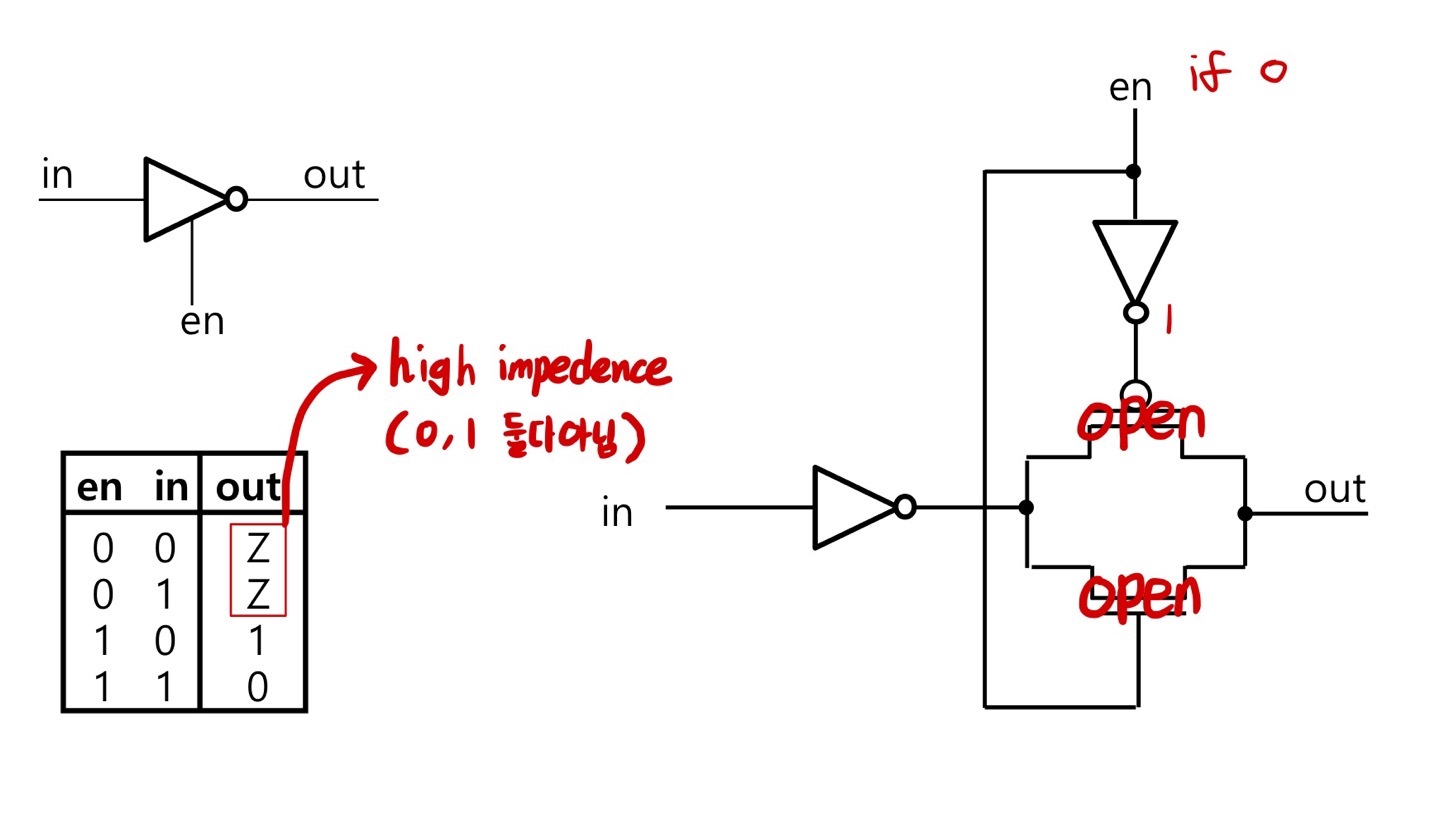

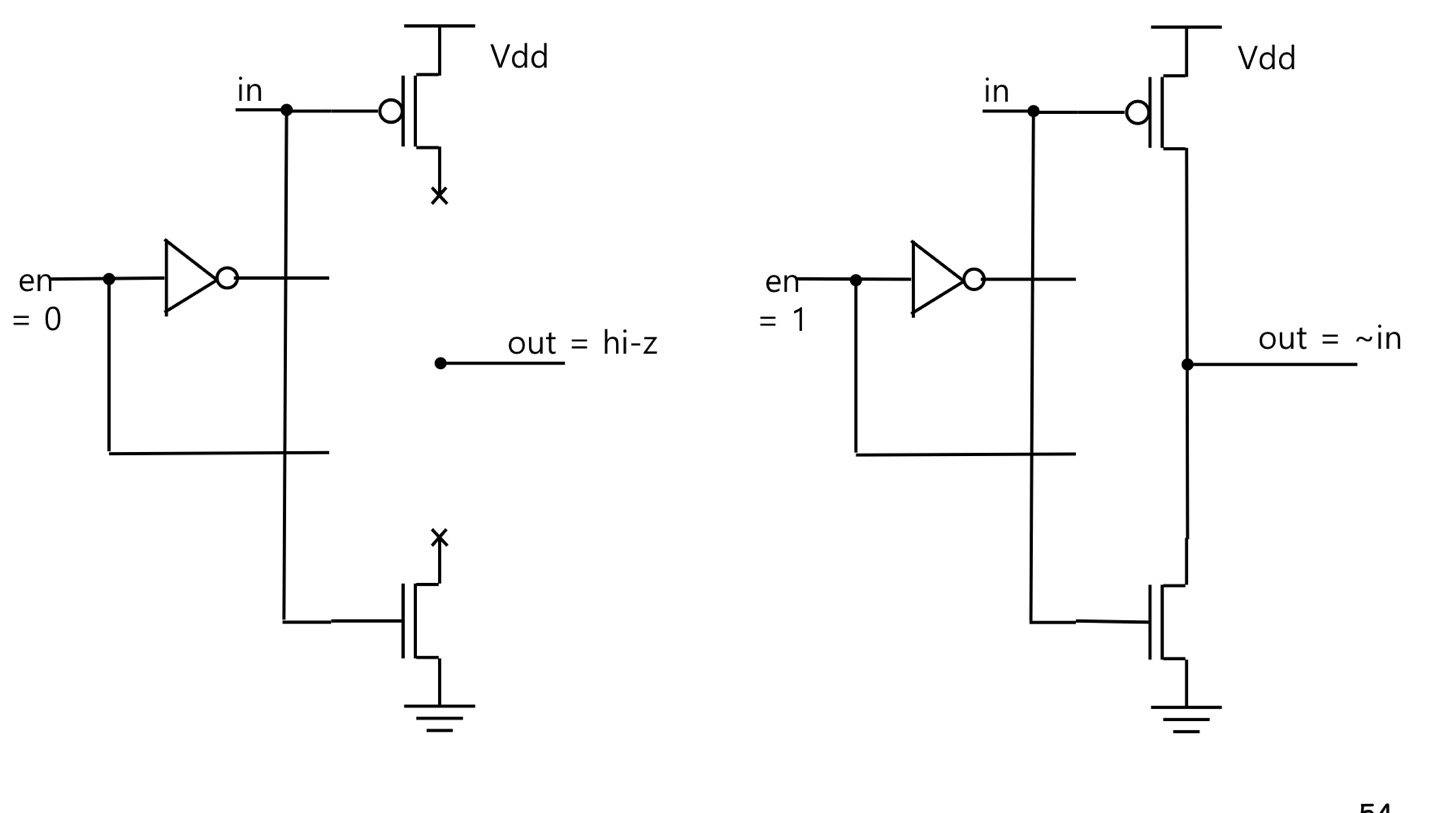

< Tri-state 인버터 >

tri-state : 0,1,high impedence 3가지 상태를 가진다.

en = 0일때 high impedence

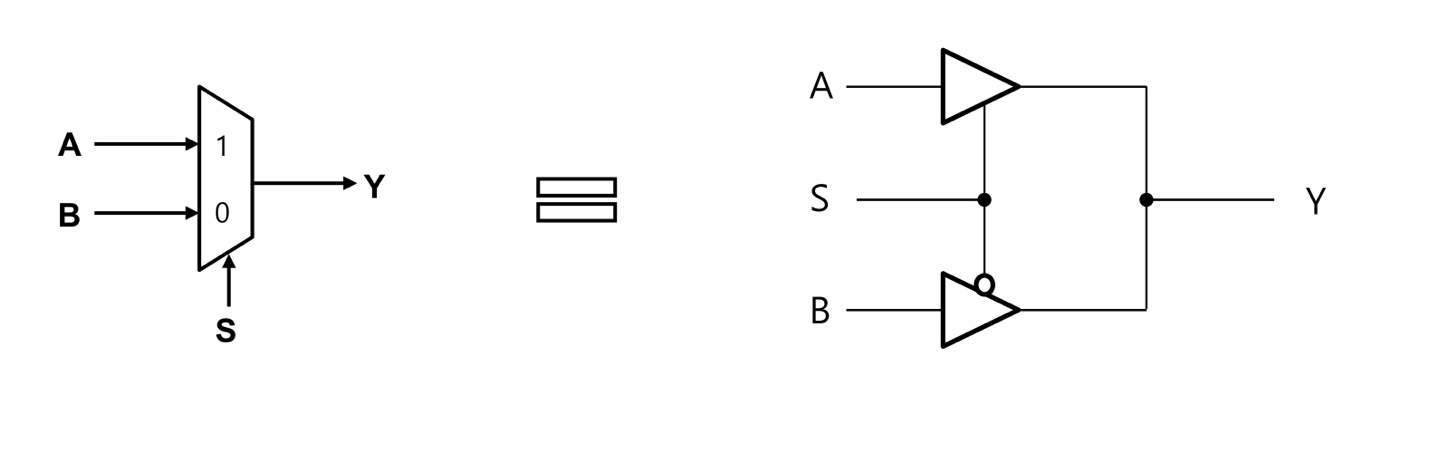

< 멀티플렉스를 이용한 tri-state buffer >

< 3상태 버퍼 사용 예 >

'Computer Architecture > 논리회로' 카테고리의 다른 글

| [11] CH8 순차논리회로 < 플립플롭(Filp-Flops) > (0) | 2022.01.08 |

|---|---|

| [10] CH8 순차논리회로 < 래치(Latch) > (0) | 2022.01.06 |

| [8] CH7 조합논리회로 < 멀티플렉서, 디멀티플렉서 > (0) | 2022.01.05 |

| [7] CH7 조합논리회로 < 인코더 > (0) | 2022.01.05 |

| [6] CH7 조합논리회로 < 디코더 > (0) | 2021.11.16 |

@Return :: Return

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[11] CH8 순차논리회로 < 플립플롭(Filp-Flops) >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbSpzd8%2Fbtrp6RRRSqe%2FAAAAAAAAAAAAAAAAAAAAAE58-e6Su4EN3VmmPF2kqop2yThhFyKlmQuiAgM2Eb3a%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DxtiSIJCNX0rRgPvZ7Hzki6CarKM%253D)

![[10] CH8 순차논리회로 < 래치(Latch) >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FclZOgr%2Fbtrp086FYsW%2FAAAAAAAAAAAAAAAAAAAAAOyoBYG6P-w7o-RssA8IUF2GfVe5d4amTZPwvFMGHIbl%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DW8isNOMQseje2De9dfaVJNWwOsw%253D)

![[8] CH7 조합논리회로 < 멀티플렉서, 디멀티플렉서 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcOvXA6%2FbtrpOxsW4Y9%2FAAAAAAAAAAAAAAAAAAAAAN5vAxsxgFDvDFN5ltBW6TTDs133S4r5AbKEIZZzxiGn%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DkbcA03ICALctzu12ZayxTQmhtoY%253D)

![[7] CH7 조합논리회로 < 인코더 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FynEV1%2FbtrpJQtqRxb%2FAAAAAAAAAAAAAAAAAAAAAAzoDlyctnr75yWL68FNaxZ1F_LknllrtVl2G2hoeIts%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DLxZ%252BU4IDvdW1eMgae5zanwipDSE%253D)