![[Verilog HDL] CH6 dataflow 모델링](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbvAJBa%2FbtrEHW6HksE%2FAAAAAAAAAAAAAAAAAAAAAM42EpFYJMdJt7Ui4IsYj6ZSZLLi0kfQIN0OVm7nBei2%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DognRMgrLIcn59v%252FbCaQMEtDC%252BJY%253D)

[Verilog HDL] CH6 dataflow 모델링UVM & RTL/Verilog HDL2022. 6. 14. 14:36

Table of Contents

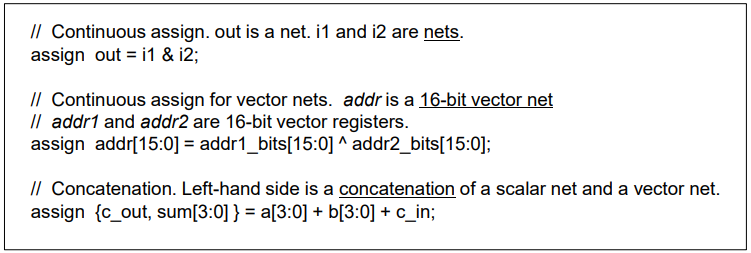

연속(Continuous)할당

연속 할당문은 데이터플로우 모델링 기법에 있어서 가장 기본이 되는 문장으로 하나의 값을 넷에 할당하는데 사용된다. 연속할당문은 키워드 assign로 시작하며, 다음과 같은 특징을 가지고 있다.

★ 규칙3 : 연속 할당문의 왼쪽은 항상 wire형이다.

- 연속 할당문은 항상 능동적이다. 할당문은 항상 오른쪽 피연산자들의 값이 바뀌자마자 왼쪽의 넷에 값을 할당한다.

- 연산자의 오른쪽에 올 수 있는 것은 레지스터 또는 넷 또는 함수 호출문이다.

- 지연값은 할당문 안에서 단위 시간으로 지정된다.

지연

지연 값은 오른쪽의 피연산자들의 값이 연산되어 왼쪽에 값을 할당할 때까지의 시간을 제어해 준다.

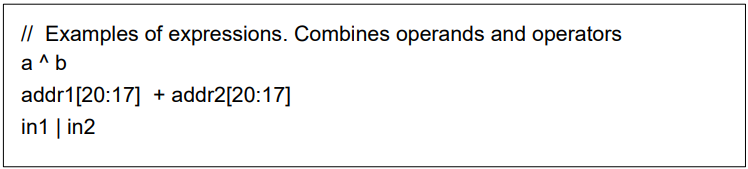

수식, 연산자 그리고 피연산자

수식

수식은 결과를 산출해 내기 위한 연산자와 피연산자들의 조합으로 이루어진다.

피연산자

연산자

연산자는 피연산자들과 함께 원하는 결과를 생성하는 역할을 한다. 다음 장에서 자세히 살펴본다.

'UVM & RTL > Verilog HDL' 카테고리의 다른 글

| [Verilog HDL] CH7 구조적 프로시저 & 절차적 할당 (0) | 2022.06.14 |

|---|---|

| [Verilog HDL] CH6 연산자 (0) | 2022.06.14 |

| [Verilog HDL] CH4 모듈과 포트 (0) | 2022.06.14 |

| [Verilog HDL] CH3 기본개념 (1) | 2022.06.14 |

| [Verilog HDL] Instruction (0) | 2022.06.10 |

@Return :: Return

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[Verilog HDL] CH6 연산자](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbsrYW5%2FbtrqGTv1qgb%2FAAAAAAAAAAAAAAAAAAAAAE2m3RKd5oN2gowEvdhXQMCN6pK9ftuRyTZpyHDJ7E2u%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DSmO3DEPbldWm4DJdWg8RuN%252BCbZ0%253D)

![[Verilog HDL] CH4 모듈과 포트](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcxiXtd%2FbtrEzKyWAWt%2FAAAAAAAAAAAAAAAAAAAAAMDowxHwtNQCqzY2QL6TXrz6NstXXG6029GWe4Q7TIqC%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3D0UIOt6MRZeykRvSOyjKwH7T7hkU%253D)

![[Verilog HDL] CH3 기본개념](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2F9xIrV%2FbtrEznQf687%2FAAAAAAAAAAAAAAAAAAAAAMpo_FZUNBckpx242-agutc3DwQfj_Br6ujoIbs1fpVg%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DCPBaDvvGS69b7FTexC7FTslz3iU%253D)