![[7] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Receive Logic](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fd0AliM%2FbtsHCSFHU4Q%2FAAAAAAAAAAAAAAAAAAAAAL1CYe4iUjsMiXIomhfb_SbkOKz1AFiwOhUCy9iOKtG3%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DBZxngqWjVo9QuFwlz8qiL0A3q0w%253D)

이 글은 제가 PCIe를 공부하면서 겪은 시행착오를 바탕으로 정리한 글입니다. PCIe를 처음 접하는 분들에게 좋은 길라잡이가 되었으면 합니다.

이전 글)

[6] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Transmit Logic

returnclass.tistory.com

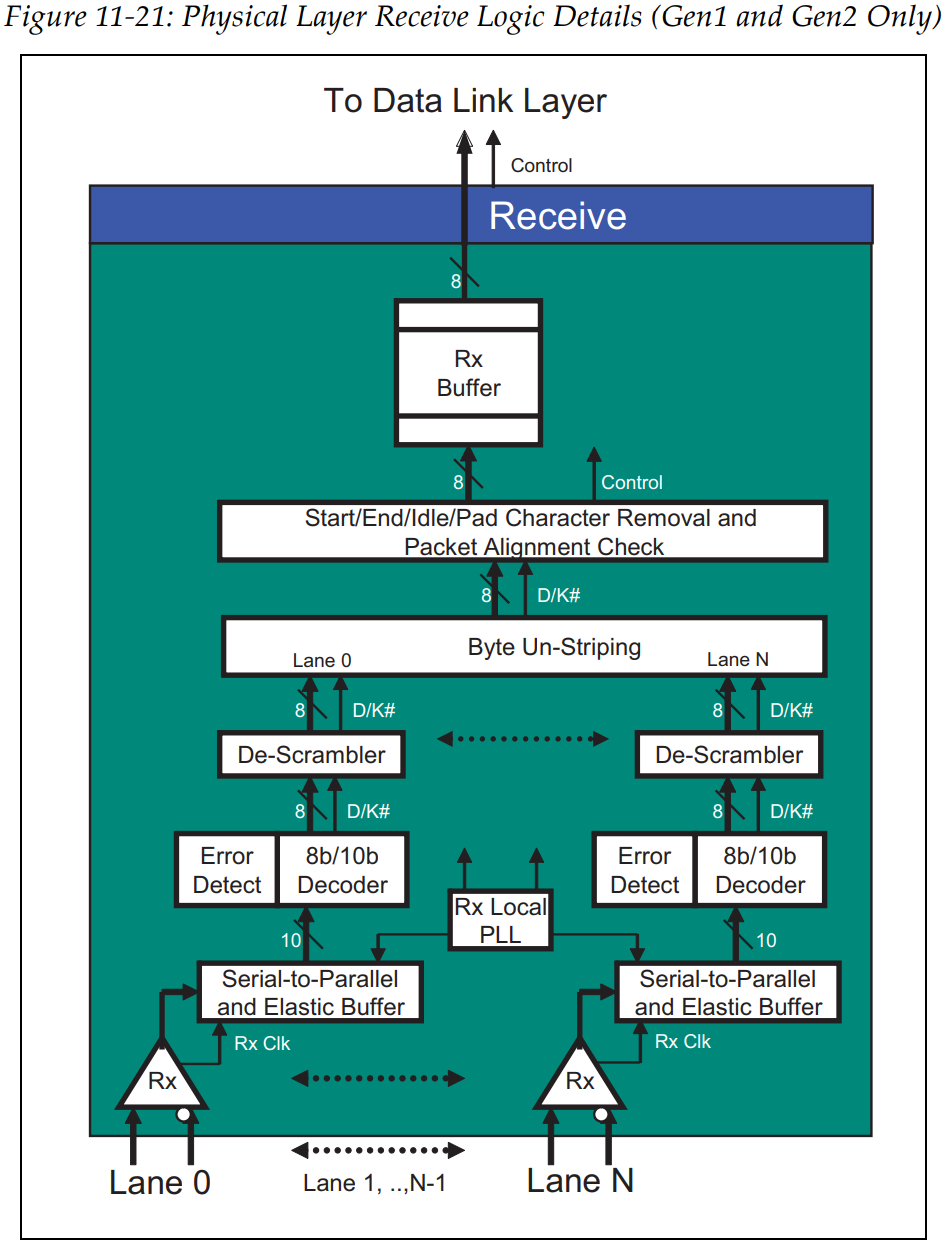

PCIe Receive Logic Details

PCIe 수신 로직은 각 레인에서 직렬로 데이터를 수신한 후 이를 데이터 링크 계층으로 전달하는 과정을 포함합니다.

Differential Receiver

수신 로직의 첫 번째 단계는 차동 입력 버퍼입니다. 이 버퍼는 각 레인의 피크-투-피크 전압 차이를 감지하여 해당 차이가 논리적 1 또는 0을 나타내는지 결정합니다. 차동 신호는 더 높은 주파수와 낮은 전압에서도 신호 무결성을 유지할 수 있게 합니다.

Rx Clock Recovery

수신기는 입력 데이터 스트림의 비트 전환을 이용해 Rx 클럭을 생성합니다. 주로 PLL(Phase-Locked Loop)을 사용합니다. 이 복구된 클럭은 송신기에서 사용한 Tx 클럭과 동일한 주파수(2.5GHz 또는 5.0GHz)를 가지며, 수신된 bit stream을 deserializer로 전송합니다.

Bit Lock 달성

8b/10b 인코딩 방식은 data stream에서 빈번한 전환(0->1, 1->0)을 포함하도록 보장하는데, 수신기 PLL은 이러한 전환을 사용해 Tx clock과 동기화된 Rx clock을 생성합니다. 수신기가 Tx 클럭 주파수에 맞추어 동기화되면 "bit lock"을 달성했다고 합니다.

- Link Training: 송신기는 TS1 및 TS2 ordered set을 길게 전송하여 수신기가 "Bit Lock"을 달성할 수 있도록 함.

Bit Lock 손실

링크가 L0s 혹은 L1과 같은 저전력 상태로 전환되면 패킷 전송이 중지되므로 수신기는 동기화를 잃습니다. 이를 오류로 간주하지 않도록 송신기는 저전력 상태로 전환하기 전에 EIOS(전기적 유휴 ordered set)를 전송하여 수신기에게 입력을 무시하도록 지시합니다.

Bit Lock 재획득

송신기가 L0s 상태에서 링크를 깨울 준비가 되면, 특정 수의 FTS ordered set을 전송합니다. 수신기는 이를 사용해 bit 및 symbol lock을 재획득합니다. FTS는 비교적 적은 수로도 회복이 가능하여 짧은 지연시간으로 복구할 수 있습니다.

- L1 상태 복구: 링크가 L1 저전력 상태에 있는 경우, 송신기는 TS1OS를 전송하여 링크를 retraining합니다. 이 과정은 L0s 상태보다 더 긴 시간이 필요합니다.

- 심각한 오류 복구: 링크에 심각한 오류가 발생하고 TLP 재전송이 4번시도 후에도 실패하면 data link layer는 physical layer에 link retraining을 요청합니다. 이 경우 bit lock은 retraining과정에서 다시 확립됩니다.

Deserializer

Deserializer는 수신된 직렬 데이터를 병렬 데이터로 변환하는 역할을 합니다. 각 레인에 도착한 데이터는 Rx 클럭에 의해 deserializer에 입력됩니다. deserializer는 10비트 sybmol을 생성하고, 이 symbol들은 elastic buffer로 전송됩니다.

Symbol Lock 달성

초기에 수신된 data stream이 구분되지 않은 bit들의 집합으로 시작됩니다. 수신 로직은 10bit symbol의 시작과 끝을 구분할 수 있어야 합니다. 이때 사용되는 것이 COM symbol입니다.

- COM symbol: 10bit encoding에서 COM symbol은 두 개의 bit와 그 뒤에 다섯 개의 반대 bit로 구성되어 있어 쉽게 감지할 수 있습니다.(e.g, 0011111010b 또는 1100000101b). 이 COM sybmol은 송신기에서 scrambling되지 않으므로 수신기에서 쉽게 인식할 수 있습니다.

COM symbol을 감지하면 수신 로직은 다음 bit가 다음 10bit symbol의 첫 번째 bit임을 알게 됩니다. 이 시점에서 deserializer가 "symbol lock"을 달성했다고 합니다.

Receiver Clock Compensation Logic

송신기와 수신기의 클럭이 정확히 같은 주파수를 가지지 않을 수 있습니다. PCIe에서 송신기와 수신기의 클럭이 정확히 일치하지 않을 수 있습니다. 이는 데이터가 너무 빨리 또는 너무 느리게 도착할 수 있는 문제를 일으킬 수 있습니다. 이러한 문제를 해결하기 위해 엘라스틱 버퍼와 SKP 심볼을 사용하여 클럭 차이를 보상합니다.

Elastic Buffer의 역할

엘라스틱 버퍼는 수신된 데이터를 일시적으로 저장하는 메모리 공간입니다. 이 버퍼는 데이터 스트림의 클럭 차이를 흡수하여 수신기가 데이터 스트림을 안정적으로 처리할 수 있도록 도와줍니다.

클럭 보상의 필요성

- 로컬 클럭: 수신기 내부에서 사용하는 클럭입니다.

- 복구된 클럭: 송신기에서 수신기로 전송된 데이터 스트림에서 복구한 클럭입니다.

두 클럭의 주파수가 약간 다를 수 있으며, 이러한 차이를 보상하지 않으면 데이터 손실 또는 중복이 발생할 수 있습니다.

상황 1: 로컬 클럭이 더 빠른 경우

로컬 클럭이 더 빠르면 엘라스틱 버퍼에서 데이터가 더 빨리 소비됩니다. 즉, 데이터가 더 빨리 클럭아웃(버퍼에서 제거)되어 버퍼가 언더플로우(빈 상태)에 가까워집니다. 이를 방지하기 위해:

- SKP 심볼 추가: 송신기에서 주기적으로 전송되는 SKIP 순서 세트(SOS)를 수신할 때, 버퍼 상태를 평가합니다. 버퍼가 비어가는 것을 감지하면, SKP 심볼을 추가하여 버퍼를 다시 채웁니다. 이렇게 하면 버퍼가 충분히 채워져서 안정적인 데이터 처리가 가능합니다.

상황 2: 복구된 클럭이 더 빠른 경우

복구된 클럭이 더 빠르면 엘라스틱 버퍼에 데이터가 더 빨리 채워집니다. 즉, 데이터가 더 빨리 클럭인(버퍼에 추가)되어 버퍼가 오버플로우(가득 참) 상태에 가까워집니다. 이를 방지하기 위해:

- SKP 심볼 제거: 버퍼가 가득 차는 것을 감지하면, SKP 심볼을 제거하여 버퍼를 비웁니다. 이렇게 하면 버퍼가 너무 빨리 가득 차지 않도록 조절하여 데이터 손실을 방지할 수 있습니다.

SKP ordered set

- 구성: SKIP 순서 세트는 COM 심볼과 세 개의 SKP 심볼로 구성됩니다.

- 삽입 규칙: 송신기는 주기적으로 SKIP 순서 세트를 전송합니다. 이러한 순서 세트는 패킷 경계에서만 삽입되며, 모든 레인에서 동시에 전송됩니다.

Lane-to-Lane Skew

스큐(Skew)는 여러 레인에 걸쳐 동시에 전송된 데이터가 수신기에 도착할 때 시간 차이가 발생하는 현상입니다. 스큐가 발생하면 수신기가 올바른 순서로 바이트를 수신하기 어려워집니다. 이를 해결하기 위해 디스큐(De-Skew)라는 과정이 필요합니다.

Oredered Set을 통한 De-Skew

oredered set는 모든 레인에 동시에 전송되며, 이들은 타이밍 불일치를 감지하는 데 유용합니다. 특히, COM 문자는 수신기가 각 레인에서 동일한 시간에 나타나는지 확인하는 데 사용됩니다. 만약 모든 레인에서 동시에 COM 문자가 나타나지 않으면, 수신기는 빨리 도착한 COM 문자를 지연시켜 모든 레인에서 일치하도록 합니다.

모든 레인에서 명확한 패턴이 필요할 때마다 디스큐를 수행할 수 있습니다. 링크 트레이닝 중에 oredered set 가 전송되며, 정상적인 링크 운영 중에는 주기적으로 SKIP oredered set 가 전송됩니다. 이들의 도착 시간을 체크하여 스큐를 지속적으로 점검할 수 있습니다. 스큐가 변화하면 링크는 복구 상태로 전환되어 이를 수정합니다. 하지만 이 과정에서 패킷이 손실되거나 재전송될 수 있습니다.

8b/10b Decoder

8b/10b 디코더는 10bit symbol stream을 8bit로 디코딩합니다. 디코더는 D 및 K table을 사용하여 변환합니다.

코드 위반 및 디스패리티 오류 감지

8b/10b 디코더는 수신된 심볼 스트림에서 불법 심볼을 감지하는 오류 감지 로직을 가지고 있습니다. 감지되는 오류 유형은 다음과 같습니다:

- 6비트 서브 블록에 4개 이상의 1 또는 0이 포함된 경우

- 4비트 서브 블록에 3개 이상의 1 또는 0이 포함된 경우

- 10비트 심볼에 6개 이상의 1 또는 0이 포함된 경우

- 10비트 심볼에 5개 이상의 연속된 1 또는 0이 포함된 경우

- 10비트 심볼이 8비트 문자로 디코딩되지 않는 경우

Descrambler

Descrambler는 8b/10b 디코더에서 데이터를 입력받아 작동합니다. 이 과정에서 descrambler는 주로 데이터(D) 문자를 descrambling 합니다. 제어(K) 문자와 ordered set은 송신기에서 scrambling되지 않으므로 descrambling 이 필요하지 않습니다.

Byte Un-Striping

Filter and Packet Alignment Check

Byte Un-Striping 로직에서 공급된 직렬 바이트 스트림은 TLP, DLLP, 논리적 유휴 시퀀스, 제어 문자(STP, SDP, END, EDB, PAD), 순서 세트를 포함합니다. 이 중 논리적 유휴 시퀀스, 제어 문자, 순서 세트는 다음 레이어로 전달되기 전에 감지 및 제거됩니다. 남은 TLP와 DLLP는 패킷의 시작과 끝을 나타내는 지표와 함께 Rx 버퍼로 전송됩니다.

Rx Buffer

Rx 버퍼는 수신된 TLP와 DLLP를 저장합니다. 시작 및 끝 문자는 제거됩니다. 수신된 패킷은 데이터 링크 계층으로 전송할 준비가 됩니다.

Reference)

- PCI Express® Base Specification Revision 5.0

- PCI Express Technology 3.0 (minshare)

'Interface Standards > PCIe' 카테고리의 다른 글

| [9] PCIe - Physical Layer (LTSSM) - 1 (0) | 2024.05.28 |

|---|---|

| [8] PCIe - Physical Layer (PCIe Gen3 ~) (0) | 2024.05.27 |

| [6] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Transmit Logic (0) | 2024.05.26 |

| [5] PCIe - Data Link Layer (DLLP & Ack/Nak protocol) (0) | 2024.05.13 |

| [4] PCIe - Transaction Layer (Ordering) (0) | 2024.05.12 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[9] PCIe - Physical Layer (LTSSM) - 1](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdcDFdw%2FbtsHF1vNnY2%2FAAAAAAAAAAAAAAAAAAAAAO4l3lophQk2kagz8bhtmDMEV0EYm-4aPno9SdEFb2WZ%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DZW1zD%252BseRJqNLXq1I%252FJCcXMIGA0%253D)

![[8] PCIe - Physical Layer (PCIe Gen3 ~)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2F1r2nf%2FbtsHCqJNKUJ%2FAAAAAAAAAAAAAAAAAAAAAAvemdzUNT-ThbkSmV_EzSHKnwaL18bGgEVxXEZbtaO-%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DBZfO6FxIZTv8EyrIx6gGEGMZCX8%253D)

![[6] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Transmit Logic](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FW6nsc%2FbtsHCz7nHNl%2FAAAAAAAAAAAAAAAAAAAAAKV9932HxRkY1u9brmQ_yz1j3q2n1BszV1KZneA17chk%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DDPuqAX6NiIQrM%252FAA%252Fs4jF1XEMT8%253D)

![[5] PCIe - Data Link Layer (DLLP & Ack/Nak protocol)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcKN1jV%2FbtsHmqqvxAB%2FAAAAAAAAAAAAAAAAAAAAAI_LQPnYH-t8kn_quxjzYG46KIz1HMXJEVFxFnd3eVhH%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DDhNFw8nOK7z9fpCDR3FS0YRJr2c%253D)