![[8] PCIe - Physical Layer (PCIe Gen3 ~)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2F1r2nf%2FbtsHCqJNKUJ%2FAAAAAAAAAAAAAAAAAAAAAAvemdzUNT-ThbkSmV_EzSHKnwaL18bGgEVxXEZbtaO-%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DBZfO6FxIZTv8EyrIx6gGEGMZCX8%253D)

이 글은 제가 PCIe를 공부하면서 겪은 시행착오를 바탕으로 정리한 글입니다. PCIe를 처음 접하는 분들에게 좋은 길라잡이가 되었으면 합니다

이전 글)

[7] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Receive Logic

returnclass.tistory.com

PCIe Gen3

PCIe Gen3 사양 업그레이드의 주요 동기는 대역폭을 두 배로 늘리는 것이었습니다. 주파수를 5 GT/s에서 10 Gb/s로 단순히 두 배로 늘리는 방법은 여러 문제를 야기했습니다:

- 높은 주파수는 더 많은 전력을 소모: 더 높은 속도에서 신호 무결성을 유지하기 위한 복잡한 조건 로직(이퀄라이제이션)이 필요하며, 이는 전력 소모를 증가시킵니다.

- 고주파수에서 신호 열화: 일부 회로 기판 재료는 높은 주파수에서 신호 열화를 경험합니다. 이는 더 나은 재료와 설계 노력이 필요하며, 비용과 개발 시간을 증가시킵니다.

- 기존 인프라 사용 유지: 새로운 설계를 기존 인프라(회로 기판 및 커넥터 등)와 호환되도록 하면 보드 설계 노력과 비용을 최소화할 수 있습니다. 높은 주파수는 이러한 작업을 더 어렵게 만듭니다.

이러한 고려 사항들은 Gen3 사양에서 두 가지 중요한 변경 사항을 이끌어냈습니다:

새로운 인코딩 모델

- 8b/10b 패킷 구성: 8b/10b 인코딩에서는 제어(K) 문자가 프레임 심볼로 사용되어 수신기가 이들을 인식하여 패킷을 해석합니다.

- 128b/130b 인코딩: 이 인코딩은 전송되는 바이트에 영향을 미치지 않고, 문자를 16바이트 블록으로 그룹화하고 각 블록의 시작 부분에 2비트 동기화 필드를 추가합니다. 이 동기화 필드는 블록에 data(10b) 또는 ordered set(01b)가 포함되어 있는지 지정합니다.

정교한 신호 Equalization

두 번째 변경 사항은 물리 계층의 전기적 서브블록에 적용되며, 링크의 송신 측과 선택적으로 수신 측에서 더 정교한 신호 이퀄라이제이션을 포함합니다. Gen1 및 Gen2 구현에서는 고정된 Tx 디엠퍼시스를 사용하여 신호 품질을 유지했지만, 전송 주파수를 5 GT/s 이상으로 증가시키면 신호 무결성 문제가 더 두드러지게 됩니다. 이를 관리하기 위해 보드 레벨에서 신호 무결성을 유지하려는 노력 대신, PHY 송신기와 수신기 회로에 더 많은 부담을 주는 방식을 채택했습니다.

8.0 GT/s 인코딩 개요

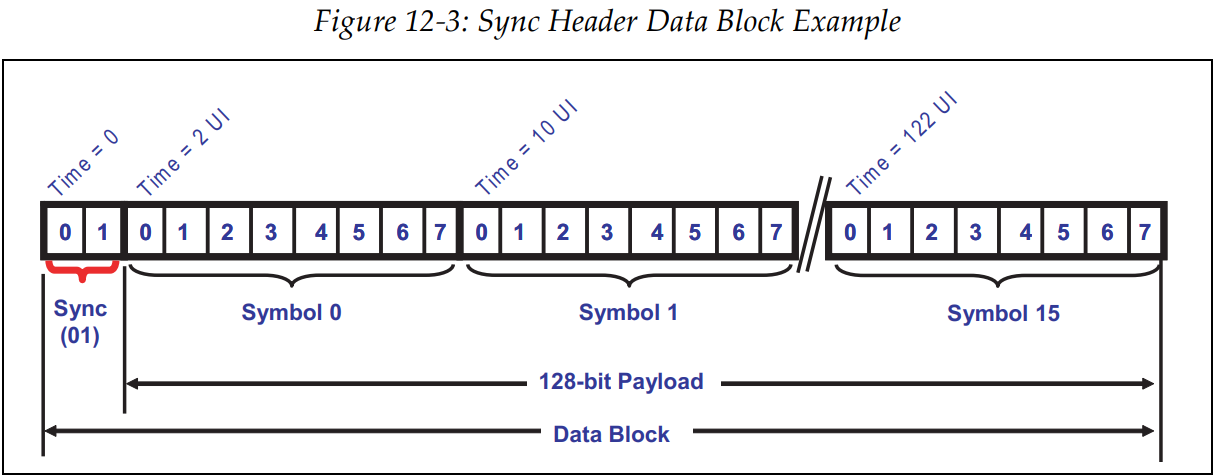

Lane-level Encoding

각 레인에서 전송되는 data block은 2bit의 sync header와 16byte(128bit) 정보로 구성됩니다. 이로 인해 총 130bit가 전송됩니다. sync header는 data block(10b) 또는 ordered set block(01b)을 나타냅니다.

Block Alignment

PCIe Gen3부터는 sync header가 각 data block 및 ordered set block의 시작 부분에 위치하여 블록 경계를 나타냅니다. EIEOS 패턴은 이러한 sync header를 인식하는 데 중요한 역할을 합니다. EIEOS 패턴은 00h와 FFh 바이트가 교대로 반복되는 특별한 패턴입니다.

EIEOS 패턴을 통한 블록 정렬 과정

EIEOS 패턴이 어떻게 sync header를 인삭하고 block 경계를 설정하는지 단계별로 알아봅시다.

- Bit Lock 달성: 수신기가 송신기의 클럭 주파수와 동기화됩니다.

- EIEOS 패턴 전송: 송신기는 EIEOS 패턴을 전송합니다.

- 수신기의 패턴 감지: 수신기는 EIEOS 패턴을 감지합니다. EIEOS 패턴은 00h와 FFh 바이트의 반복이므로, 이 고유한 패턴을 통해 수신기는 특별한 패턴이 전송되고 있음을 알 수 있습니다.

- Sync header 인식: EIEOS 패턴이 감지된 후, 수신기는 이 패턴 뒤에 오는 데이터를 분석하여 동기화 헤더를 찾습니다. 즉, 수신기는 EIEOS 패턴의 끝을 인식하면, 그 다음에 오는 bit를 sync header로 인식합니다.

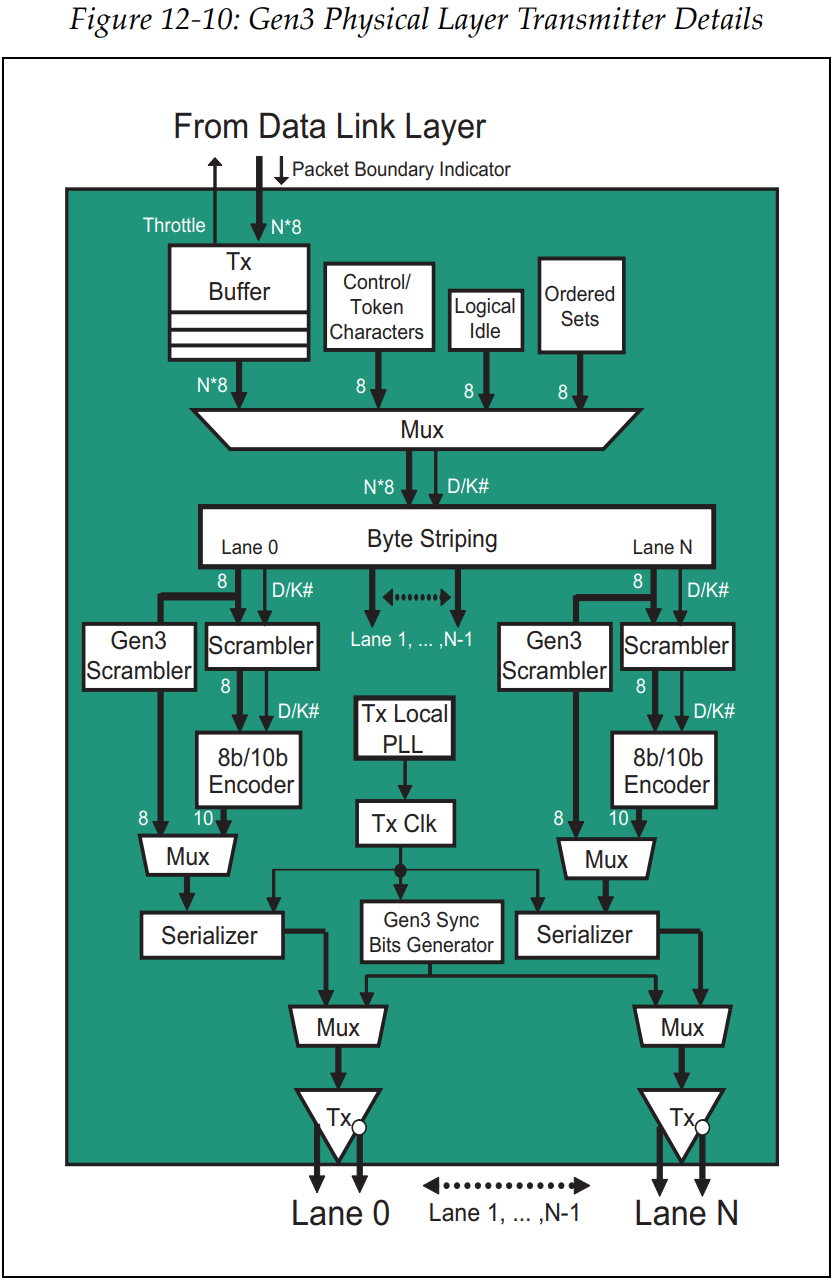

Transmit Logic

Framing Token

PCIe Gen3부터는 데이터 블록에 나타날 수 있는 다섯가지 framing token이 정의되어 있습니다.

- STP - Start TLP: TLP의 시작을 나타내며, 전체 패킷의 길이를 포함하고 있습니다.(단위: DW)

- SDP - Start DLLP: DLLP의 시작을 나타냅니다. (DLLP는 길이가 고정)

- EDB - End Bad: TLP가 무효화된 경우에 사용됩니다.

- EDS - End of Data Stream: data stream의 마지막 DW를 나타냄.

- IDL - Logical Idle: link가 idle 상태일 때 전송되는 0바이트 데이터.

Mux

TLP와 DLLP는 data link layer에서 logical phy로 도착합니다. mux에서는 STP 또는 SDP 토큰을 추가하여 완전한 TLP/DLLP를 만듭니다.

- Gen3 TLP 경계: TLP경계는 TLP 패킷의 시작 부분에 있는 STP 토큰의 길이 필드로 정의됩니다. 따라서 END 프레이밍 토큰이 더 이상 필요하지 않습니다.

- Data Stream 종료: data stream이 종료하거나 SOS를 전송하기 전에 EDS토큰을 data stream에 추가합니다.

- 정기적인 SOS 삽입: Skip 타이머에 따라 mux에서는 정기적으로 SOS를 data stream에 삽입합니다.

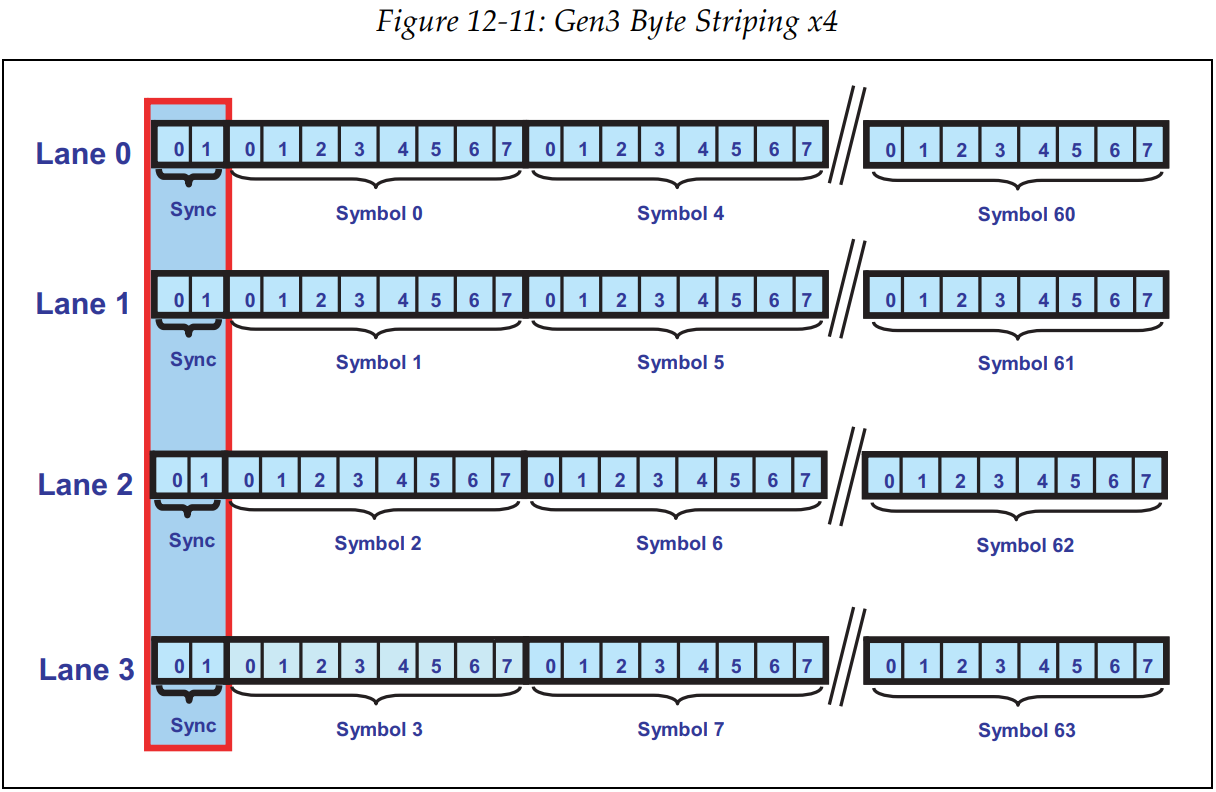

Byte Striping

Byte Striping은 전송될 바이트를 모든 사용 가능한 레인에 분산시킵니다.

Scrambler

이전 세대와 동일하게 LFSR기반으로 scrambling을 진행합니다. (다만 알고리즘 자체는 동일하지 않습니다.)

Serializer

이전 세대와 동일하게 작동하지만, 10bit가 아닌 8bit를 한 번에 처리.

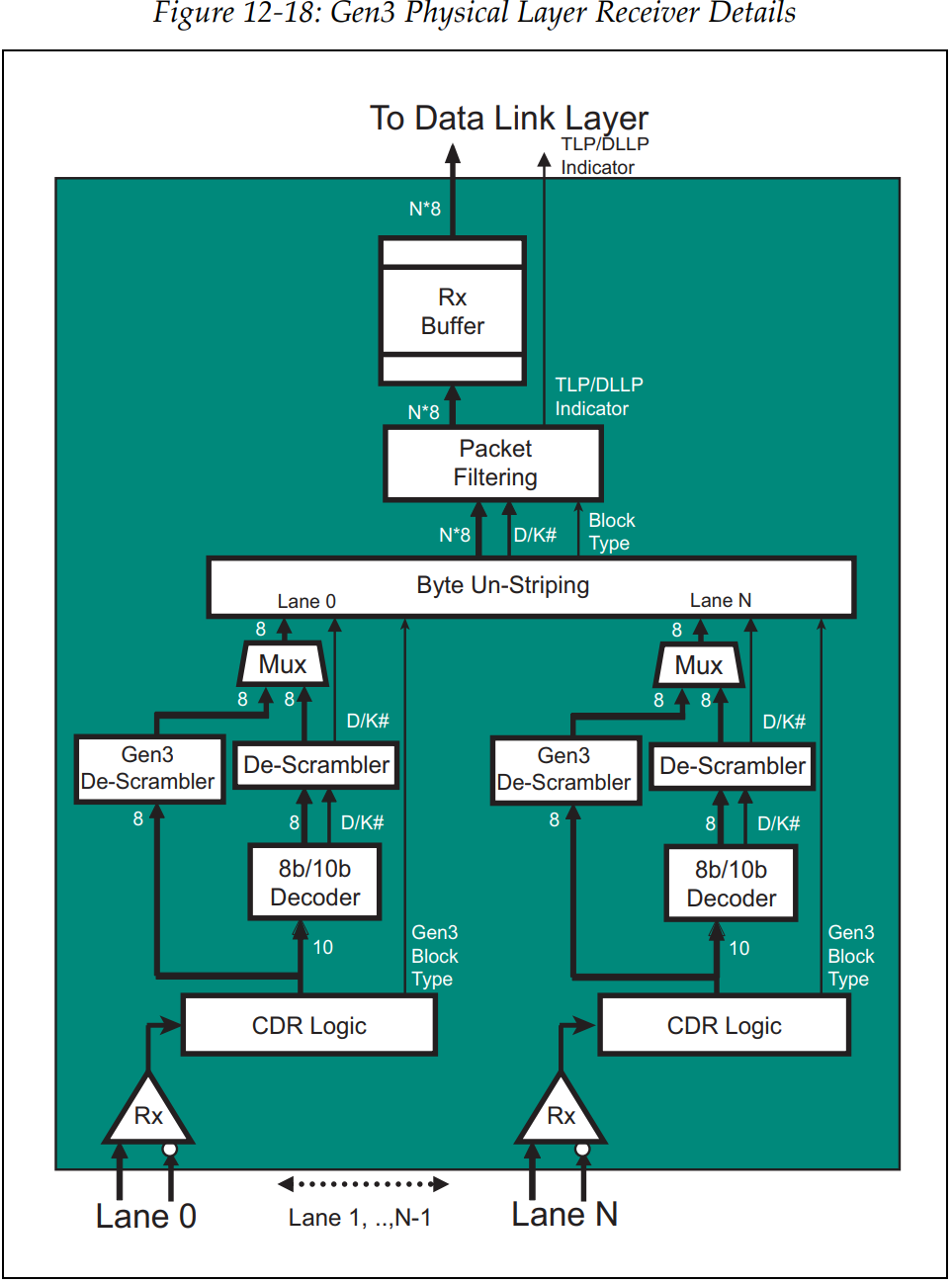

Receive Logic

이전 세대와 유사하게 동작하지만, 더 높은 속도와 효율성을 위해 몇 가지 변경 사항이 있는데,

- CDR(Clock and Data Recovery)회로: 수신기는 PLL(Phased-Locked Loop)을 사용하여 송신기의 클럭 주파수에 동기화됩니다. 이를 통해 복구된 클럭(Rx Clock)을 생성하고, 이 클럭을 사용하여 들어오는 비트를 deserializer에 래치합니다. 블록 정렬이 설정 된 후, 8bit symbol을 elastic buffer에 래치합니다.

- 데이터 처리: Descrambler는 scrambling된 문자를 복원하고, 바로 byte un-stripping 로직으로 전달됩니다. 마지막으로, ordered set은 필터링되고, 남은 TLP 및 DLLP가 data link layer로 전달됩니다.

Deserializer

들어오는 data는 복귀된 Rx 클럭에 의해 각 lane의 serial-parallel 변환기로 들어갑니다. 8bit symbol은 elastic buffer로 들어갑니다.

Block 정렬 달성

트레이닝 중에 전송된 EIEOS는 130bit bock의 경계를 식별하는 역할을 합니다. 이 과정을 통해 수신기는 세 단계로 진행되는데,

- Unaligned 단계: 전기적 유휴 상태 후, 수신기는 EIEOS 패턴을 감지하여 블록 경계를 조정합니다.

- Aligned 단계: 수신기는 EIEOS를 계속 감시하고 블록 경계를 조정합니다. SDS(Data stream 시작) ordered set을 감지하면 Locked 단계로 진행됩니다.

- Locked 단계: 수신기가 이 단계에 도달하면 더 이상 블록 경계를 조정하지 않습니다.

블록 유형 감지

블록 정렬이 달성되면, 수신기는 들어노는 블록의 첫 두 bit를 검사하여 블록 유형(data block / ordered set block)을 식별합니다. Ordered set 블록은 physical layer에서만 처리되며, data block은 상위 layer로 전달됩니다.

Receiver Clock Compensation Logic

Elastic Buffer

수신된 symbol은 복구된 클럭을 사용하여 엘라스틱 버퍼에 클럭되고, 수신기의 로컬 클럭을 사용하여 엘라스틱 버퍼에서 클럭 아웃됩니다. 엘라스틱 버퍼는 주파수 차이를 보상하기 위해 SKP symbol을 추가하거나 제거합니다.

Lane-to-Lane Skew

multi-lane인 경우 데이터가 도착하는 시점이 lane마다 조금씩 다를 수 있습니다. 수신기에서는 이를 조정할 필요가 있습니다. 초기 도착한 데이터를 클럭 수만큼 지연시켜 늦게 도착한 것들과 맞추는 작업을 합니다.

Descrambler

수신기(Receiver)는 송신기(Transmitter)와 동일한 방식으로 scrambling 다항식을 생성합니다. 수신기는 입력 데이터에 동일한 값을 XOR연산하여 원래 정보를 복원합니다. 송신기와 마찬가지로 수신기는 각 lane에 대해 별도의 LFSR을 구현하거나 혹은 하나의 LFSR만 사용할 수 있습니다.

Byte Un-Striping

이 로직은 이전 세대와 동일하게 적용됩니다.

Packet Filtering

Byte Un-Striping에서 제공되는 직렬 byte stream에는 TLP, DLLP, IDL, Ordered Set이 포함될 수 있습니다. 여기서 IDL과 ordered set은 phy에서 제거되고 data link layer로 전달되지 않습니다.

Rx Buffer

Rx buffer는 수신된 TLP와 DLLP를 data link layer가 수용할 수 있을 때까지 보관합니다.

Reference)

- PCI Express® Base Specification Revision 5.0

- PCI Express Technology 3.0 (minshare)

'Interface Standards > PCIe' 카테고리의 다른 글

| [10] PCIe - Physical Layer (LTSSM) - 2 (0) | 2024.06.24 |

|---|---|

| [9] PCIe - Physical Layer (LTSSM) - 1 (0) | 2024.05.28 |

| [7] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Receive Logic (0) | 2024.05.26 |

| [6] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Transmit Logic (0) | 2024.05.26 |

| [5] PCIe - Data Link Layer (DLLP & Ack/Nak protocol) (0) | 2024.05.13 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[10] PCIe - Physical Layer (LTSSM) - 2](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fbk0lNb%2FbtsIbrUR2RL%2FAAAAAAAAAAAAAAAAAAAAAHmv2BIWvjyWHVtbiKK-7gziHRx6KomyGU4W7z7JE0nH%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DfNAwEPQ8UH9fzfa9NOukojbRxfU%253D)

![[9] PCIe - Physical Layer (LTSSM) - 1](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdcDFdw%2FbtsHF1vNnY2%2FAAAAAAAAAAAAAAAAAAAAAO4l3lophQk2kagz8bhtmDMEV0EYm-4aPno9SdEFb2WZ%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DZW1zD%252BseRJqNLXq1I%252FJCcXMIGA0%253D)

![[7] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Receive Logic](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fd0AliM%2FbtsHCSFHU4Q%2FAAAAAAAAAAAAAAAAAAAAAL1CYe4iUjsMiXIomhfb_SbkOKz1AFiwOhUCy9iOKtG3%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DBZxngqWjVo9QuFwlz8qiL0A3q0w%253D)

![[6] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Transmit Logic](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FW6nsc%2FbtsHCz7nHNl%2FAAAAAAAAAAAAAAAAAAAAAKV9932HxRkY1u9brmQ_yz1j3q2n1BszV1KZneA17chk%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DDPuqAX6NiIQrM%252FAA%252Fs4jF1XEMT8%253D)