![[10] PCIe - Physical Layer (LTSSM) - 2](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fbk0lNb%2FbtsIbrUR2RL%2FAAAAAAAAAAAAAAAAAAAAAHmv2BIWvjyWHVtbiKK-7gziHRx6KomyGU4W7z7JE0nH%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DfNAwEPQ8UH9fzfa9NOukojbRxfU%253D)

이 글은 제가 PCIe를 공부하면서 겪은 시행착오를 바탕으로 정리한 글입니다. PCIe를 처음 접하는 분들에게 좋은 길라잡이가 되었으면 합니다.

LTSSM은 아주 방대한 내용을 담고 있습니다. 이번 글에서 모든 내용을 담기보다는 각각의 state가 가진 핵심 동작 위주로 설명할 것입니다. 자세한 내용은 PCIe Specification을 참고해주세요.

이전 글)

[9] PCIe - Physical Layer (LTSSM) - 1

returnclass.tistory.com

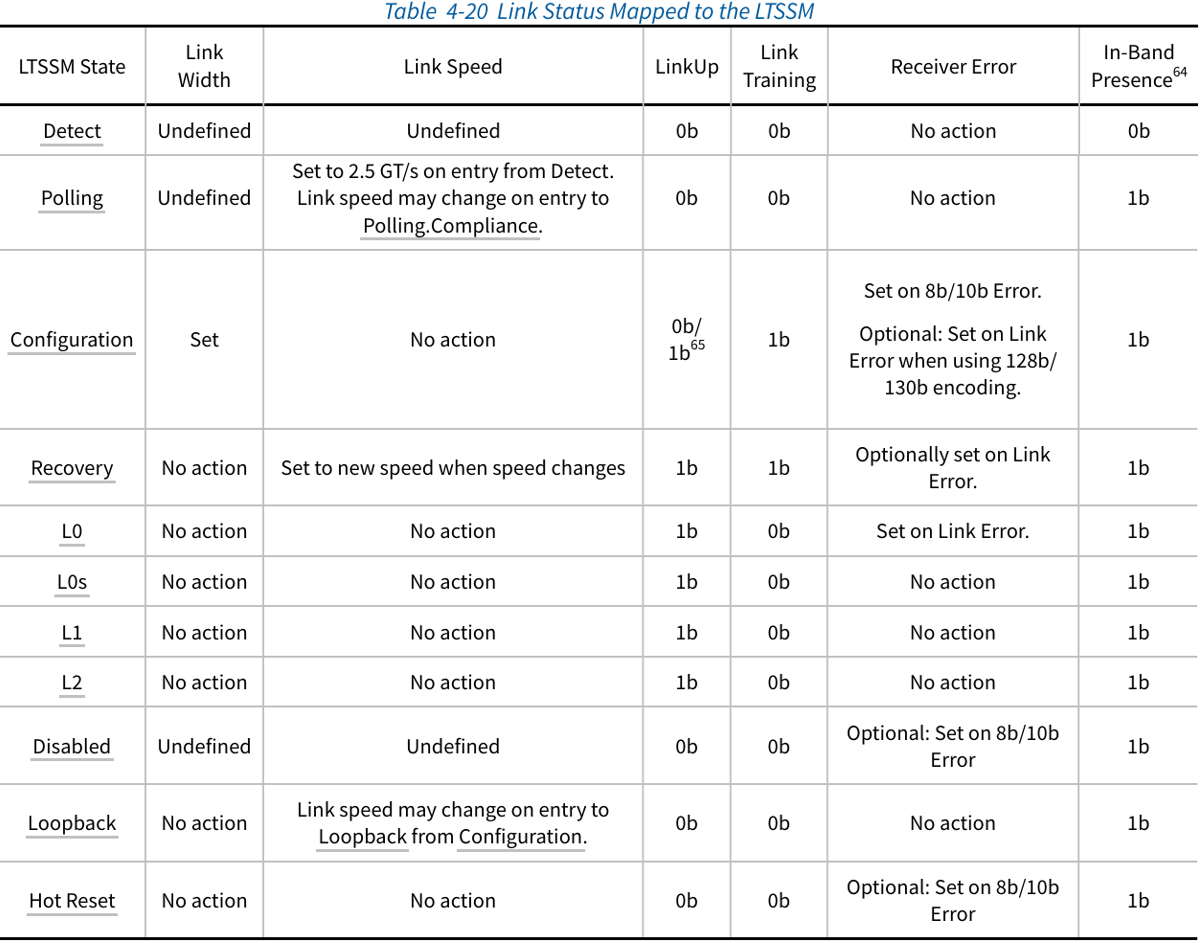

Detect State

Detect state의 목표는 state의 이름과 같이 link partner를 감지하는 과정입니다.

Detect.Quiet

일종의 reset과 같은 동작입니다. linkup, link training bit등 link status와 관련된 register들을 초기화합니다. link가 electrical idle 상태가 아니거나 12ms TIMEOUT이 발생한 경우 Detect.Active state로 전이합니다.

Detect.Active

펄스를 보내서 반대편 누군가(링크 파트너)가 있는 것이 확인합니다. 모든 lane에서 detect 되지 않은 경우 다시 Detect.Quiet로 전이되며, 하나 이상의 lane에서 링크파트너가 감지된 경우 Polling 상태로 전이합니다.

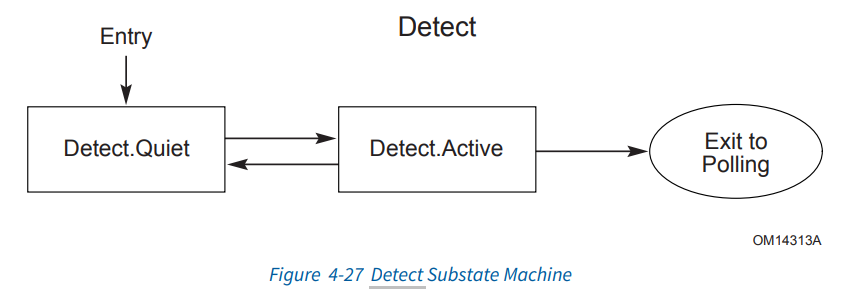

Polling State

Polling state의 목표는 link의 speed를 2.5GT/s로 설정하며, bit/symbol lock을 확보하는 데 있습니다. 이는 link를 training하는 과정에 필수적인데, 예를 들어 PCIe 5.0을 지원하는 link라고 해도, 한 번에 32.0GT/s의 속도로 설정할 수 없으며, 처음에는 2.5GT/s로 설정한 다음, recovery.speed 상태에서 지원하는 속도로 전환하기 때문입니다. 또한 "lock"을 달성하는 것도 굉장히 중요한데, lock을 달성했다는 것은 쉽게 말해서 링크 파트너와 대화를 할 수 있다는 뜻입니다. bit lock은 1과 0을 판별할 수 있다는 것, symbol lock은 1byte symbol을 구분할 수 있다는 것입니다. 이렇게 lock을 달성함으로써 링크 파트너간 TLP와 DLLP와 같은 packet을 주고 받을 수 있습니다.

Polling.Active

송신기는 TS1 OS(Ordered Set)을 모든 lane에 보내는데, 여기서 lane과 link 번호는 다음 상태인 Configuration(Polling.Configuration 아님)에서 설정할 것이기 때문에 PAD로 설정되며, 이때 TS1의 Speed rate 필드에 속도를 표기하며, 최소 1024개의 TS1 OS를 전송합니다.

송신기가 다시 8개의 TS1 or TS2 OS를 수신하면 Polling.Configuration 상태로 전환합니다. 만약 24ms동안 수신하지 못하면 Detect 상태로 돌아갑니다. 별개로 compliance bit가 설정되면 Polling.Compliance상태로 전환합니다.

Polling.Compliance

쉽게 말해서, test를 하기위해 사전에 정의된 특정 패턴을 전송하며, 특정 패턴에 대한 조건이 만족되면, Polling.Active 상태로 다시 전환됩니다.

Polling.Configuration

송신기는 TS2 OS를 모든 레인에 보내며, 마찬가지로 lane과 link 번호는 다음 상태인 Configuration 상태에서 설정할 것이기 때문에 PAD값으로 설정됩니다. 마찬가지로 송신기가 8개의 연속적인 TS2 OS를 다시 수신하면(일종의 handshake) Configuration 상태로 전환합니다. 또한 48ms 동안 위 조건을 충족하지 못하면 Detect 상태로 돌아갑니다.

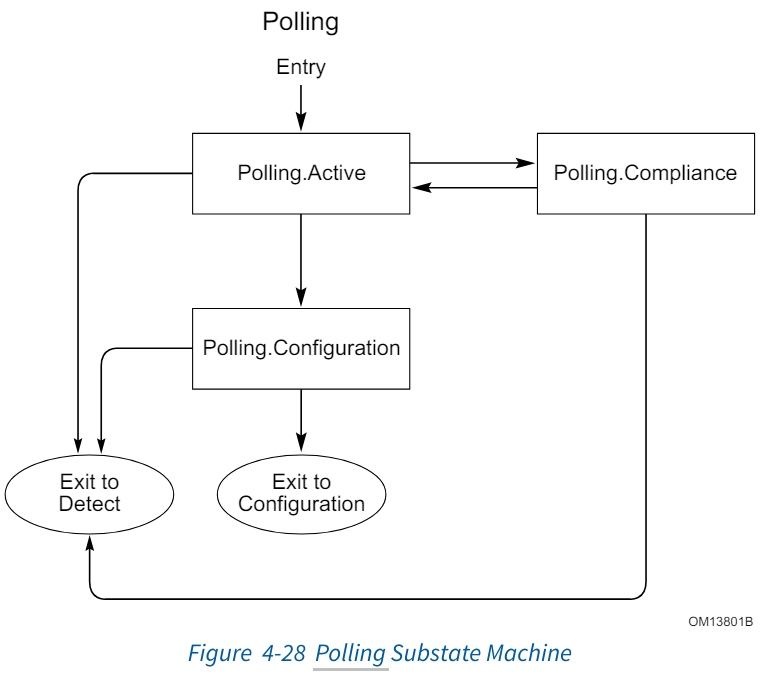

Configuration State

Configuration 상태의 목표는 link와 lane 번호를 설정하는 것입니다. 송신기 입장에서 Detect 상태를 통해 다른 편에 누군가 있다는 것을 알고 있으며, Polling 상태를 통해 그 누군가와 대화할 수 있습니다. 이제 그 누군가와 대화함으로써, link와 lane 정보를 설정하는 것입니다.

Configuration.Linkwidth.Start

Downstream 및 Upstream lane으로 향하는 모든 경로에 link 번호를 설정한(non-PAD) TS1 OS를 주고 받으며, TS1 handshake가 발생하면, Configuration.Linkwidth.Accept 상태로 전환합니다.

Configuration.Linkwidth.Accept

이제 Lane 번호를 설정한 TS1 OS를 downstream device로 전송하며, 이때 Configuration.Lanenum.Wait로 전환합니다.

Configuration.Lanenum.Wait

마찬가지로 TS1 OS handshake가 발생하면 Configuration.Lanenum.Accept 상태로 전환합니다.

Configuration.Lanenum.Accept

지금까지의 TS1 OS handshake를 바탕으로 링크파트너들은 lane 정보와 link 정보를 서로 알게되었습니다. 최종인 확인을 하기 위해서 이번에는 TS2 OS를 주고받습니다. 이때 Configuration.Compete으로 상태를 전환합니다.

Configuration.Compete

최종적인 TS2 OS handshake가 발생하면 Configuration.Idle로 전환합니다.

Configuration.Idle

Idle 패킷을 수신한뒤, L0 상태로 전환합니다.

L0 State

Linkup bit을 1로 설정하여, Link가 활성화됨을 나타냅니다. 동시에 L0상태에서 다른 상태로 전환하는 경우가 있을 수 있는데:

Recovery 상태로의 전환

여러가지 이유로 L0 상태에서 Recovery 상태로 전환될 수 있습니다. 대표적으로 speed 변경, link width 변경, link error 복구등이 있습니다. 앞서 PCIe data link layer에서 ACK/NAK 프로토콜을 설명할때, 특정 TIMEOUT이 발생할 경우 link의 상태를 Recovery상태로 바꾼다고 했습니다. PCIe의 link 오류는 대부분 단발적인 경우가 많은데 이렇게 연속적으로 에러가 발생한다는 것은 link 자체에 문제가 있기 때문에 PCIe의 link 상태를 recovery 상태를 바꿔 re-training을 시키는 것입니다. 또 다른 대표적인 상황은 link의 속도 변경입니다. 앞서 말했듯이 PCIe 링크가 32.0 GT/s로 지원하더라도 한 번에 32.0GT/s로 link가 동작할 수는 없습니다. link training 초기에는 2.5GT/s 속도로 동작하다가 recovery 상태로 전환후, 원하는 속도로 변경해야되기 때문입니다.

L0s 상태로의 전환

PCIe link의 전력 절감을 위해 전환하는 모드로, 빠른 L0 복귀가 가능하다는 장점이 있습니다. 특정 상태를 거칠 필요없이 특정 숫자의 FTS ordered set을 전송한 뒤, L0상태로 복귀할 수 있습니다. 이때 보내야할 FTS OS 수는 전에 link training 할때 TS OS의 FTS# 필드에 기록한 값입니다.

L1 상태로의 전환

중간 정도로 전력 소모가 낮은 상태로, L0 상태로 돌아오기 위해서는 Recovery 상태를 거쳐야 합니다.

L2 상태로의 전환

가장 전력 소모가 낮은 상태로, L0상태로 돌아오기 위해서는 Detect 상태부터 다시 시작해야합니다.

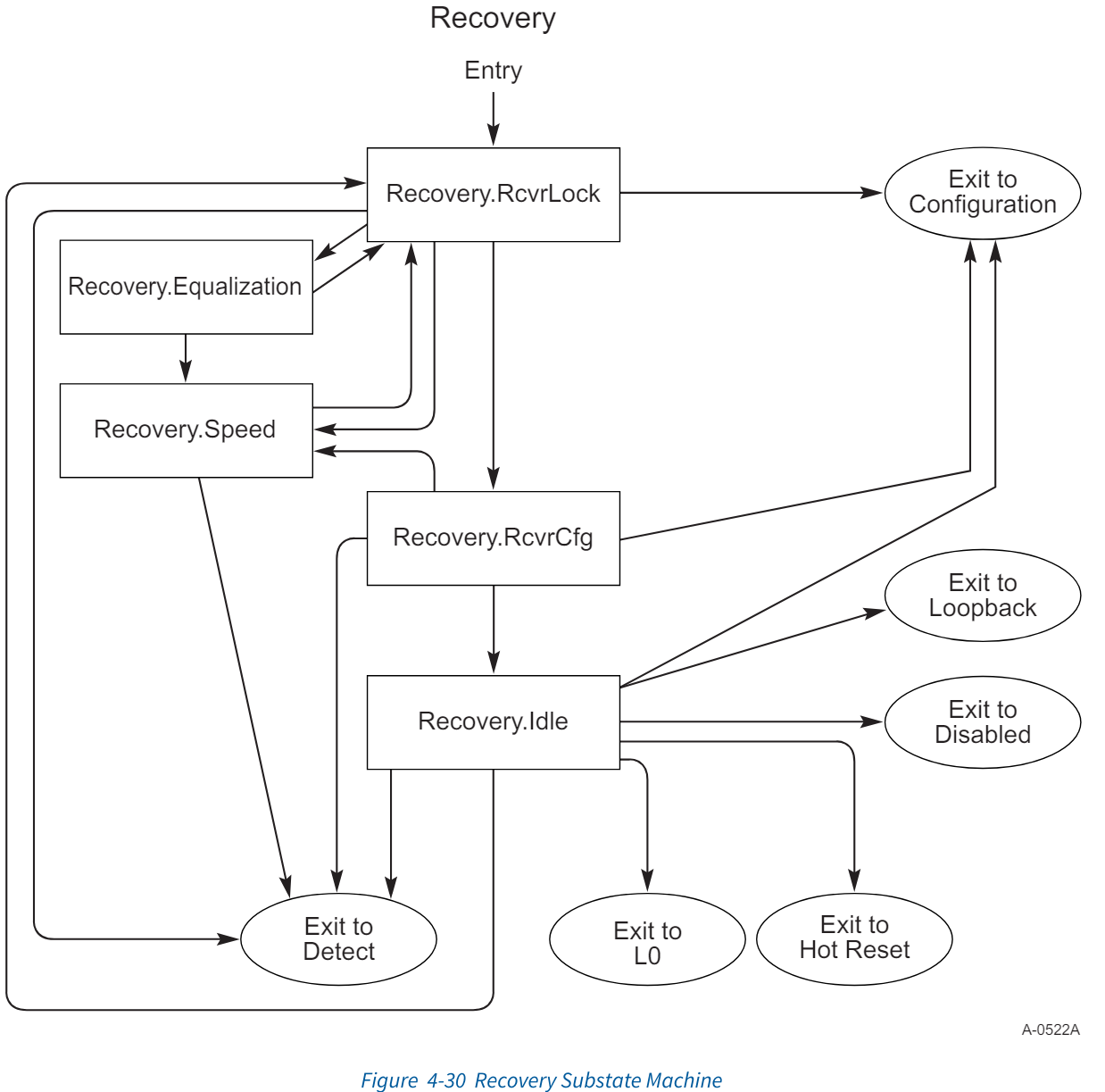

Recovery State

Recovery.RcvrLock

Recovery.RcvrLock 상태에서 현재 link의 속도가 8.0 GT/s 이상인 경우는 block lock을 달성하기 위한 동작을 수행합니다. Configuration에서 bit 및 symbol lock을 이미 달성했으며, PCIe gen 3부터 block 개념이 도입되었으므로 PCIe gen3의 링크 속도인 8.0GT/s 이상일때만 block lock을 추가적으로 실시합니다. 이를 위해 TS1 OS를 주고 받습니다.

Recovery.RcvrCfg

Recovery.RcvrLock에서 TS1 handshake가 일어났다면, Recovery.RcvrCfg에서는 TS2 handshake가 일어납니다.

Recovery.Speed

Recovery.Speed 상태에서 TS OS의 Rate ID 필드에 설정된 속도로 링크의 속도를 전환합니다. 만약 전환하려는 링크의 속도가 8.0 GT/s 이상이라면 Equalization 프로세스를 진행합니다.

Recovery.Equalization

Equalization 과정은 쉽게 말해서 링크의 신호 품질을 fine-tuning하는 것입니다. 신호 품질의 우수함을 측정하는 조건은 BER(Bite Error Ratio)이며, 특정 BER(10**-12)을 충족하면 Equalization 과정을 종료합니다.

Recovery.Idle

Idle 패킷을 올바르게 수신하면, 변경된 속도로 L0상태로 돌아갈 수 있습니다.

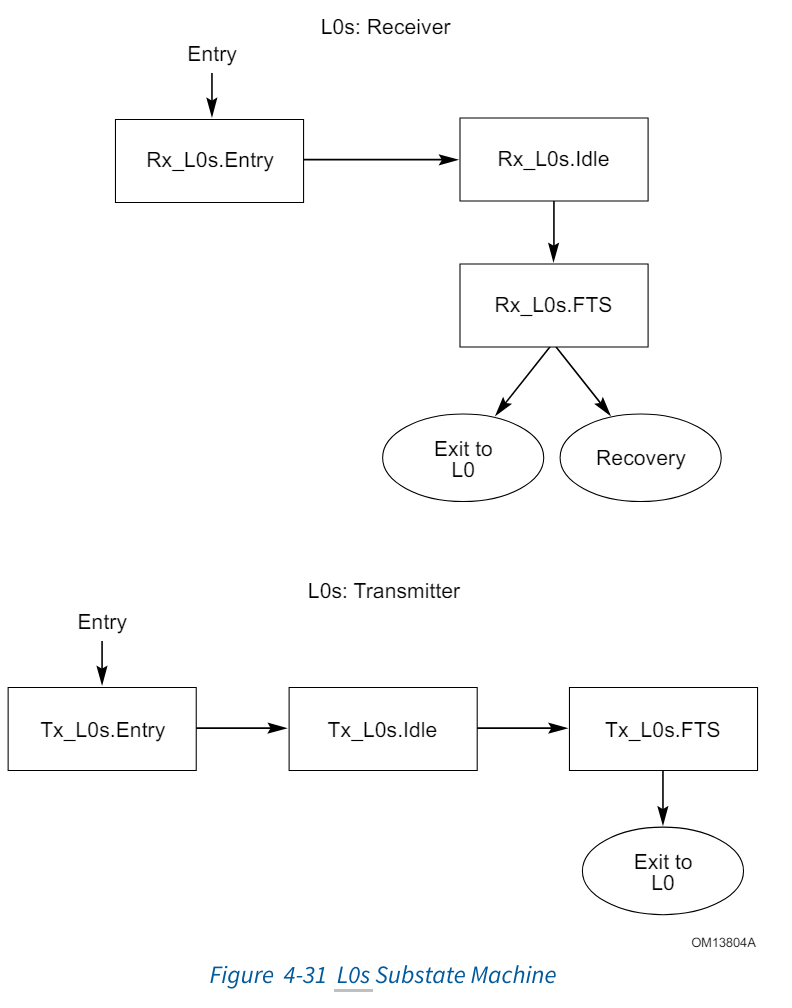

L0s State

Receiver L0s

Rx_L0s.Entry

송신기가 최소한의 전기적 유휴 상태(TTX-IDLE-MIN) 후 Rx_L0s.Idle로 전환합니다.

Rx_L0s.Idle

전기적 유휴 상태에서 벗어나거나 100ms 타임아웃 후 Rx_L0s.FTS로 전환합니다.

Rx_L0s.FTS

사전에 정의된 FTS 수 만큼 수신하면 L0로 전환. 만약 N_FTS timeout이 발생하면 Recovery로 전환합니다.

Transmitter L0s

Tx_L0s.Entry

EIOSQ를 보내고 전기적 유휴 상태로 전환 후 Tx_L0s.Idle로 전환(T[TX-IDLE-MIN]).

Tx_L0s.Idle

지시받으면 Tx_L0s.FTS로 전환합니다.

Tx_L0s.FTS

모든 lane에서 N_FTS 만큼의 OS를 전송한 후 L0로 전환합니다.

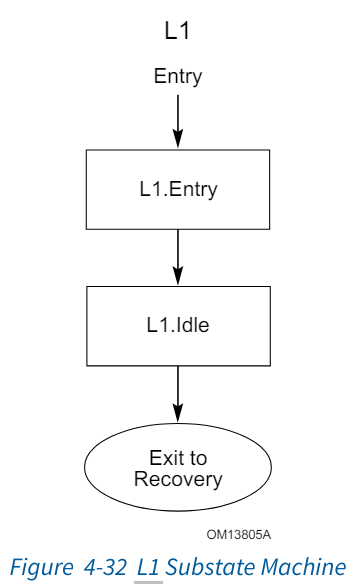

L1 State

L1.Entry

EIOS를 송수신하여 링크가 electrical idle상태로 전환하며, LTSSM은 T(TX-IDLE-MIN) 이후 L1.Idle로 전환합니다.

L1.Idle

링크가 electrical idle 상태를 벗어나며, LTSSM의 state는 Recovery state로 전환

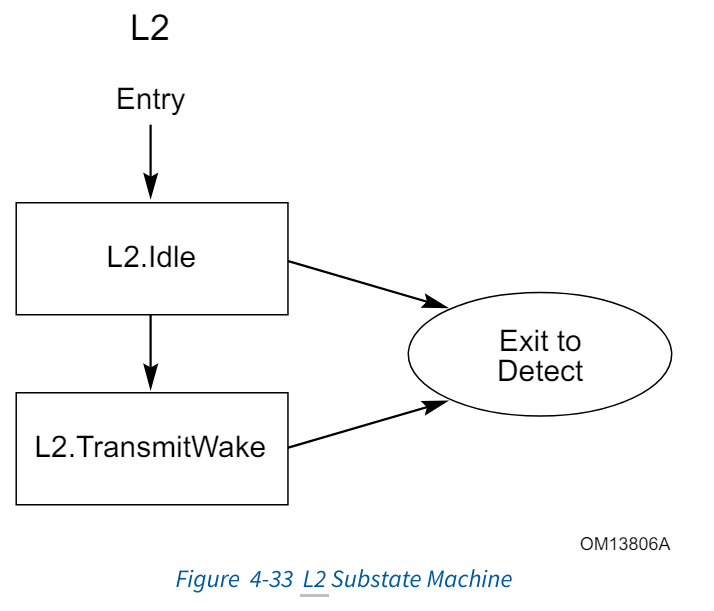

L2 State

L2.Idle

L1과 마찬가지로 EIOS를 송수신하여 PCIe 링크를 electrical idle 상태로 전환하며, Beacon이라는 특정 상태에서 통신을 복구하기 위해 사용되는 신호를 수신했을때 LTSSM의 state를 L2.TransmitWake로 전환합니다.

L2.TransmititWake

PCIe 링크를 electrical idle 상태를 exit하며, Detect 상태로 전환합니다.

Disabled State

말 그대로 disabled 상태이며 linkup bit를 0으로 클리어하며, 모든 레인에 대하여 disabled bit을 설정한 채로 16~32개의 TS1 OS를 전송하고, electrical idle 상태로 전환합니다. 최소 하나 이상의 레인에서 EIOSQ를 수신하면 Detect 상태로 전화되며, 별도로 2ms Timeout이 발생하더라도 detect 상태로 전환합니다.

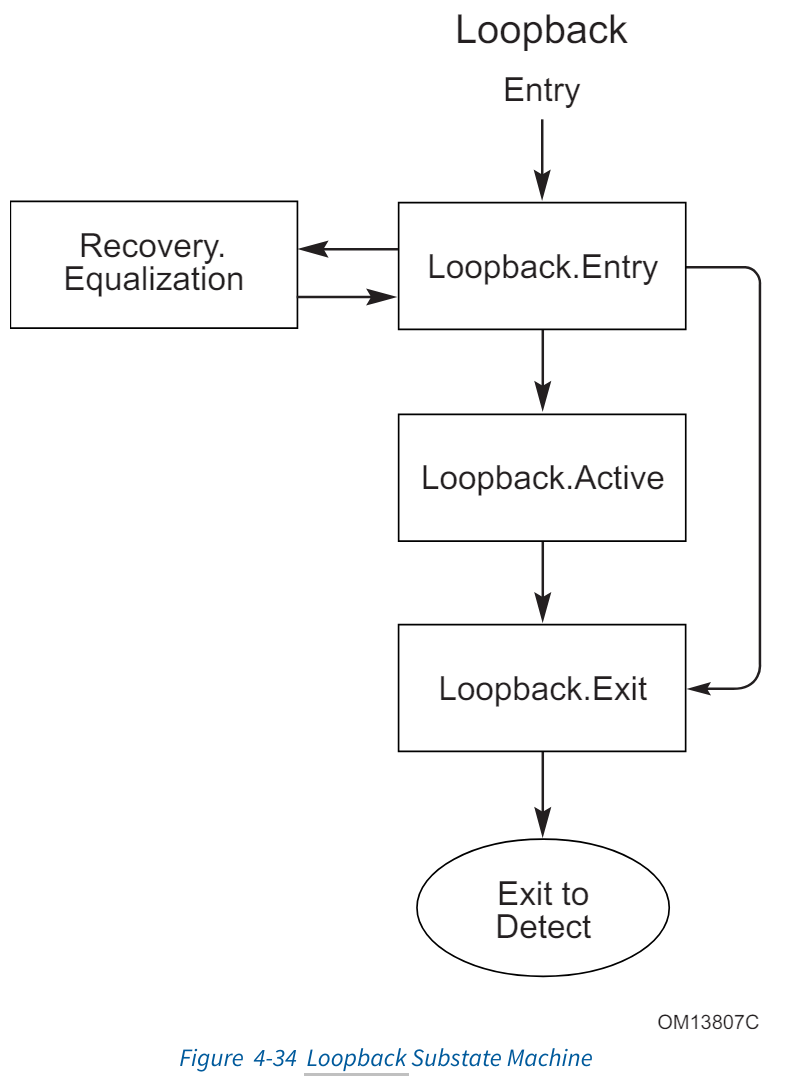

Loopback State

주로 link의 test관련해서 사용되는 상태입니다. Configuration 또는 Recovery 상태에서 진입하며 주요 동작은 LinkUp bit를 0으로 설정하고, Loopback bit를 설정한 TS1 OS를 송수신합니다. 그 후, 상태를 Loopback.Active로 전환하며, 이 상태에서 4개 연속된 EIOS를 수신하거나 상위 계층의 지시를 따라 Loopback.Exit로 전환됩니다.

Hot Reset State

실행 중 downstream들의 link를 재설정을 수행하는 단계이며, 보통 “Hot” 이라는 용어가 붙으면 run-time 중 어떤 것을 한다는 의미로 생각하면 됩니다. 모든 lane에 Hot Reset bit를 설정한 후 TS1 OS를 전송하며, 이를 수신하면 LinkUp bit이 0으로 설정됩니다. 2ms Timeout이 발생하면 Detect로 전환됩니다.

Reference)

- PCI Express® Base Specification Revision 5.0

'Interface Standards > PCIe' 카테고리의 다른 글

| [12] ATS (Address Translation Service) (0) | 2025.01.13 |

|---|---|

| [11] PHY Interface for the PCI Express 간단히 알아보기 (0) | 2024.08.12 |

| [9] PCIe - Physical Layer (LTSSM) - 1 (0) | 2024.05.28 |

| [8] PCIe - Physical Layer (PCIe Gen3 ~) (0) | 2024.05.27 |

| [7] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Receive Logic (0) | 2024.05.26 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[12] ATS (Address Translation Service)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdaolaK%2FbtsLNxpS0PM%2FAAAAAAAAAAAAAAAAAAAAAMbDX-XX2q4w5dAH2lk0L5lhOdSHVCZq6YWZ_yL94vrH%2Ftfile.dat%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DHwpNSZ0FVcEy9NoVH4Gsdg3%252BFaw%253D)

![[11] PHY Interface for the PCI Express 간단히 알아보기](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FejVgVs%2FbtsI1FZZYR7%2FAAAAAAAAAAAAAAAAAAAAAOmQJJt9K0BlmhYgB4fzX4UQklIhjqP24V189vY1xv8U%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3Dp59wLtxPXNguDMylAYvf%252B4bm9wA%253D)

![[9] PCIe - Physical Layer (LTSSM) - 1](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdcDFdw%2FbtsHF1vNnY2%2FAAAAAAAAAAAAAAAAAAAAAO4l3lophQk2kagz8bhtmDMEV0EYm-4aPno9SdEFb2WZ%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DZW1zD%252BseRJqNLXq1I%252FJCcXMIGA0%253D)

![[8] PCIe - Physical Layer (PCIe Gen3 ~)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2F1r2nf%2FbtsHCqJNKUJ%2FAAAAAAAAAAAAAAAAAAAAAAvemdzUNT-ThbkSmV_EzSHKnwaL18bGgEVxXEZbtaO-%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DBZfO6FxIZTv8EyrIx6gGEGMZCX8%253D)