![[5] CH7 조합논리회로 < 가산기 , 비교기 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FTrxMI%2Fbtrk7FboOsI%2FAAAAAAAAAAAAAAAAAAAAAL6JZJV2BrmdmAGuvIKnsdR-kVGNO5owXmmwe6DSgk_a%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DhThQjORgz%252FpiB%252FAM481iUla34pI%253D)

조합논리회로는 AND,OR,NOT 세 가지 기본 논리회로의 조합으로 만들어지며, 입력신호 논리게이트 및 출력신호로 구성된다. 논리게이트는 입력신호를 받아서 출력신호를 생성하며, 이과정에서 2진 입력데이터를 조합하여 원하는 2진 출력 데이터를 생성한다.

이번 장에서는 조합논리회로의 기본이 되는 가산기(adder),비교기(comparator),디코더(decoder),인코더(encoder),멀티플렉서(multiplexer),디멀티플렉서(demultiplexer),코드 변환기(code converter)등의 회로를 설계하는 방법과 이들 회로를 이용하는 방법에 대해서 알아본다.

가산기

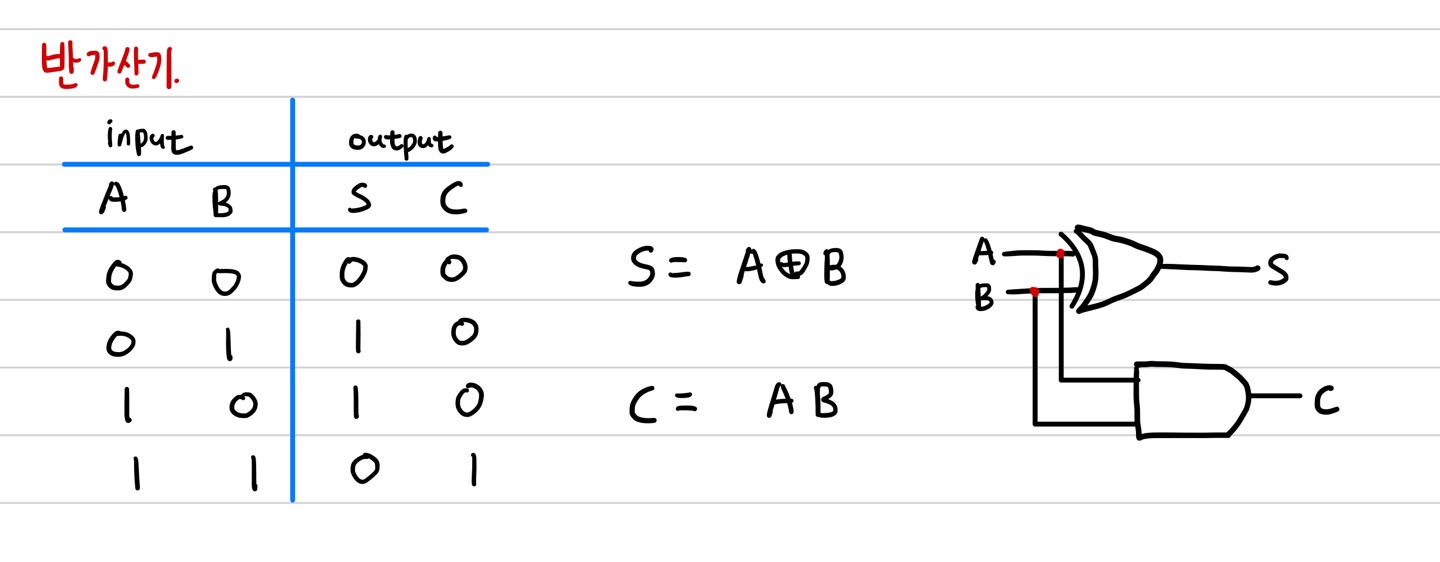

1. 반가산기

한 자리 2진수 2개를 입력하여 합과 캐리를 계산하는 덧셈 회로. 캐리C는 입력A,B모두 1인 경우에만 1이 되고, 합 S는 입력 A,B둘 중 하나만 1일때 1이 된다.

2. 전가산기

반가산기는 2진수 한자리 덧셈을 하므로 아랫자리에서 발생한 캐리를 고려하지 않기 때문에 2비트 이상의 2진수 덧셈을 할 수 없다. 이캐리를 고려하여 만든 덧셈 회로가 전가산기입니다. 전가산기는 두개의 2진 입력 A,B와 아랫자리로부터 올라온 캐리를 포함하여 한 자리 2진수 3개를 더하는 조합논리회로이다.

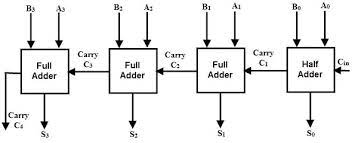

3. 병렬가감산기

전가산기 여러 개를 병렬로 연결하여 2비트 이상인 가산기를 만들 수 있으며, 이를 병렬 가산기(parallel-adder)이라 한다. 다음 그림은 4비트 병렬가산기로 입력 A,B가 각각 4비트이며 전가산기의 최하위 비트의 캐리는 0을 입력한다. 계산 결과 합은S3S2S1S0이며, 마지막 캐리는 C4이다.

이 병렬 가산기의 B입력을 다음 그림에서 처럼 부호S(Sign)와 XOR하여 전가산기의 입력으로 사용하면 덧셈과 뺄셈이 모두 가능 하다. 즉, S=0이면 B의 값이 그대로 전가산기로 입력되어 덧셈이 되고, S=1이되면 B의 값이 반전, 즉,1의 보수가 되어 입력된다. 또한 뺄셈의 경우(S=1) 맨 오른쪽 전가산기의 캐리 입력 C0=1이 되어 결과적으로 B의 1의 보수에 1이 더해져서 2의 보수가 만들어진다. 이 회로를 병렬가감산기 회로라 한다.

4. 고속가산기

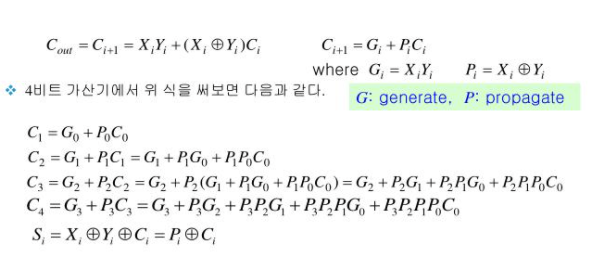

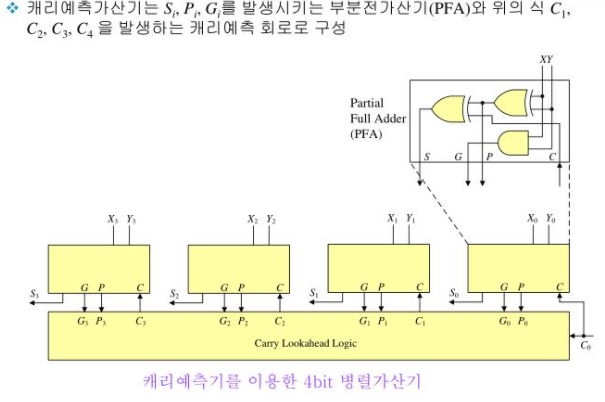

디지털 시스템에서 속도는 매우 중요한 요소이다. 대표적으로 가산기를 생각해보자. 위의 병렬가산기는 속도가 매우 느리다. 왜냐하면 아랫단에서 윗단으로 전달되는 캐리 때문이다. 이를 리플-캐리라 한다. 아랫단 가산기의 결과가 나와야만 바로 윗단을 계산할 수 있기 때문이다. 즉, 하나의 전가산기에서 캐리가 나오기까지 게이트4개(XOR2개,AND,OR)를 거치며, 3단계에 걸쳐 최종 출력이 나오게 된다. 전가산기 한 개를 지날 때마다 점점 더 지연이 심해짐을 알 수 있다. 이것을 해결하기 위해 캐리예측가산기(CLA)를 사용한다. 이는 캐리를 미리 계산하여 위로 보내는 것이다. i단에서 발생한 캐리의 논리식은 A,B모두 1일때, 또는 A,B 둘 중 하나가 1이고 C(i)가 1일때 캐리가 발생하므로 C(i+1)의 논리식은 다음과 같다.

5. BCD 가산기

BCD코드는 2진수와 달리 표현 범위가 0에서9까지 이므로 BCD계산을 하려면 결과를 보정해야 한다.

2진수 합의 결과가 1010~1111인 경우 보정해야 되고 예를 들어 6+7=13인 경우 1101에서 6을 더해준 1 0011으로 보정한다.

비교기

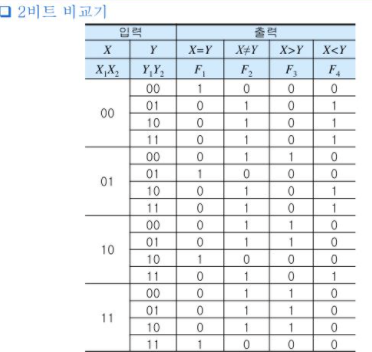

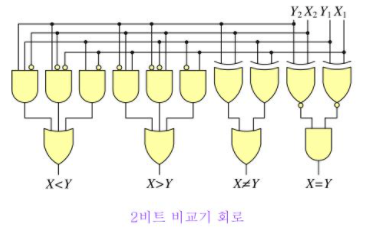

2진 비교기는 두 2진수 값의 크기를 비교하는 회로이다. 먼저 1비트 비교기를 살펴보자.

다음은 2비트 비교기 이다.

'Computer Architecture > 논리회로' 카테고리의 다른 글

| [7] CH7 조합논리회로 < 인코더 > (0) | 2022.01.05 |

|---|---|

| [6] CH7 조합논리회로 < 디코더 > (0) | 2021.11.16 |

| [4] CH6 논리식의 간소화 (0) | 2021.11.16 |

| [3] CH5 불 대수 (0) | 2021.11.08 |

| [2] CH4 논리 게이트 (0) | 2021.11.07 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[7] CH7 조합논리회로 < 인코더 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FynEV1%2FbtrpJQtqRxb%2FAAAAAAAAAAAAAAAAAAAAAAzoDlyctnr75yWL68FNaxZ1F_LknllrtVl2G2hoeIts%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DLxZ%252BU4IDvdW1eMgae5zanwipDSE%253D)

![[6] CH7 조합논리회로 < 디코더 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FkJOD7%2Fbtrk9sb3ChB%2FAAAAAAAAAAAAAAAAAAAAAD7GZoFjjmrVNER2caCzw-jfZXFjDbCDk5sD1ff7QOR3%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DpBJZ56ozzkuwprbF8JGci88f8Qs%253D)

![[4] CH6 논리식의 간소화](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbZVLIh%2Fbtrk4lkbuHN%2FAAAAAAAAAAAAAAAAAAAAAFqTCfPCjBt-fsu8B830NAQGvsQUuHEEqf5350-dZZdi%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3Dm1IDEF%252Bchck3ENbwaVszfiyu44E%253D)

![[3] CH5 불 대수](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FkUh6R%2Fbtrj3W6w0SR%2FAAAAAAAAAAAAAAAAAAAAAHauOjnr096968R-RM-ayCggTSeVApeXuLI00dfQe6Mp%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DW8pxg2xQxXEjXvCbUyMX10ipPtM%253D)