![[15] CH8 순차논리회로 < 카운터 FSM 설계-3 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FesLF8c%2FbtrqaJMnq3K%2FAAAAAAAAAAAAAAAAAAAAAAvYg6H9zAXDZFi1gBkT0xrXpToeEGSZCc0xgF662ohc%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DH6XNkdfIVRLmEAn1v68ksrVb9P4%253D)

[15] CH8 순차논리회로 < 카운터 FSM 설계-3 >Computer Architecture/논리회로2022. 1. 9. 15:27

Table of Contents

< 클럭 분주기의 개념 >

- 주파수를 나누는 블록

- 예를들어, 100MHz/2 = 50MHz로 클럭이 느려짐

- 반대로 주기는 늘어남 1/100MHz =10ns, 1/50MHz =20ㅜㄴ

- 디지털 회로로 쉽게 만들 수 있음

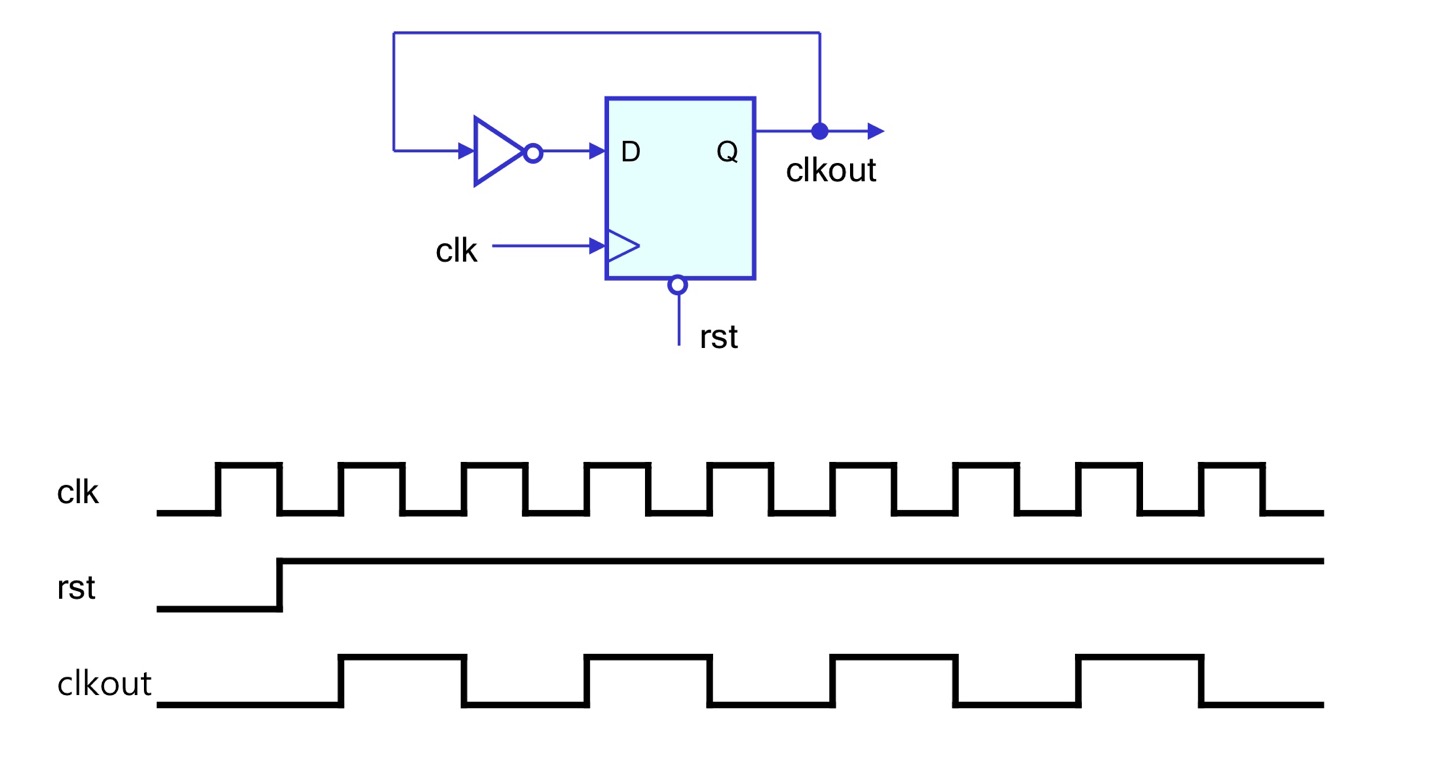

< 클럭 2분주기 >

- 매 클럭 에지마다 값을 바꾸기 때문에 입력 클럭을 2분주한 클럭을 발생

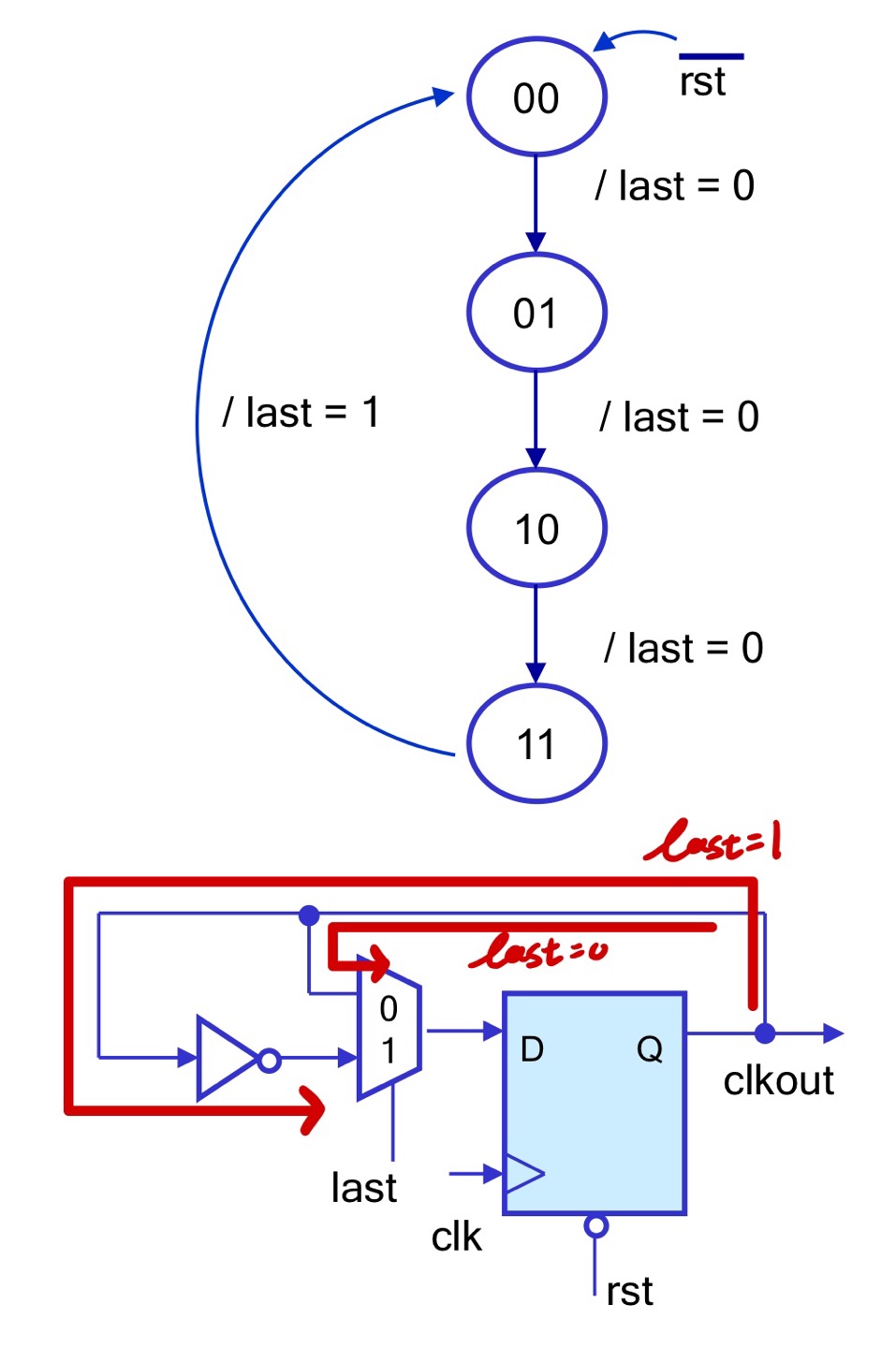

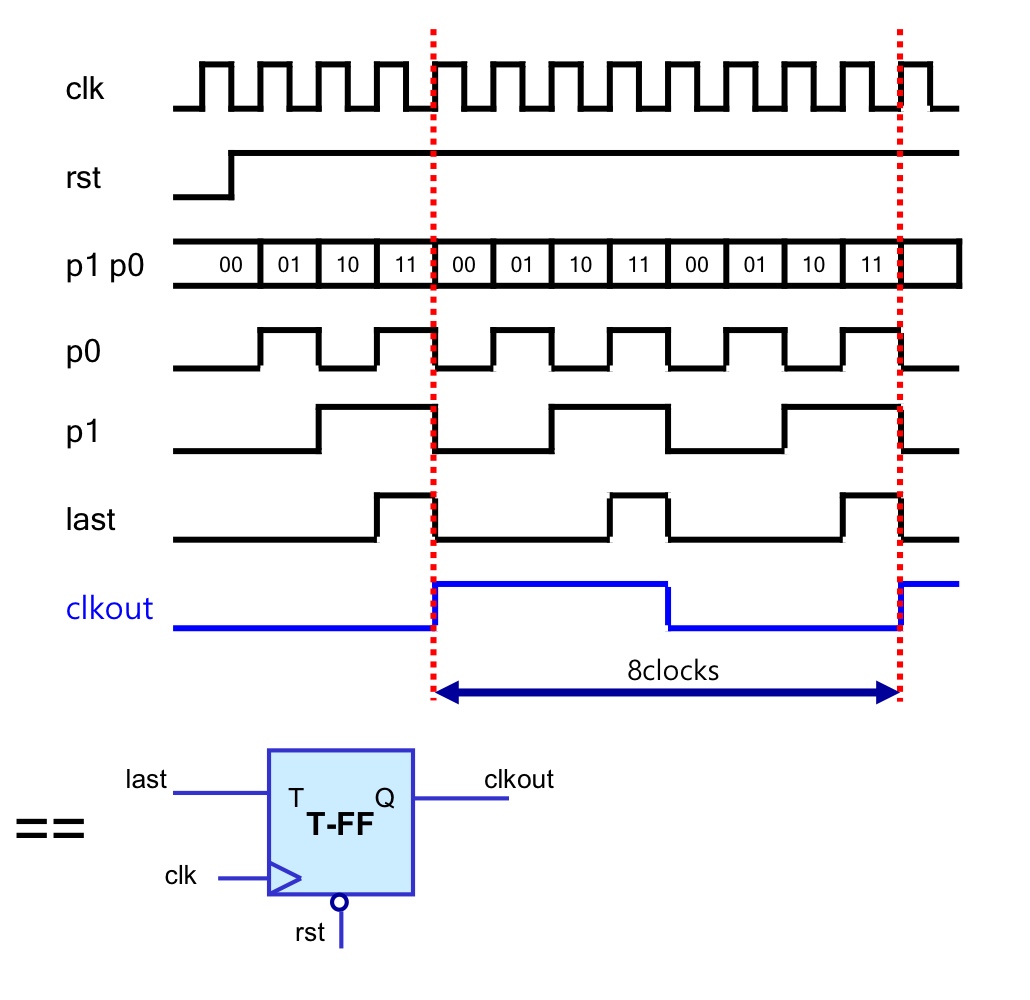

< 클럭 8분주기 >

- 00>01>10>11로 변하는 카운터가 11이 되었을 때만 last=1

- last =1일 경우에만 clkout이 반전된다.

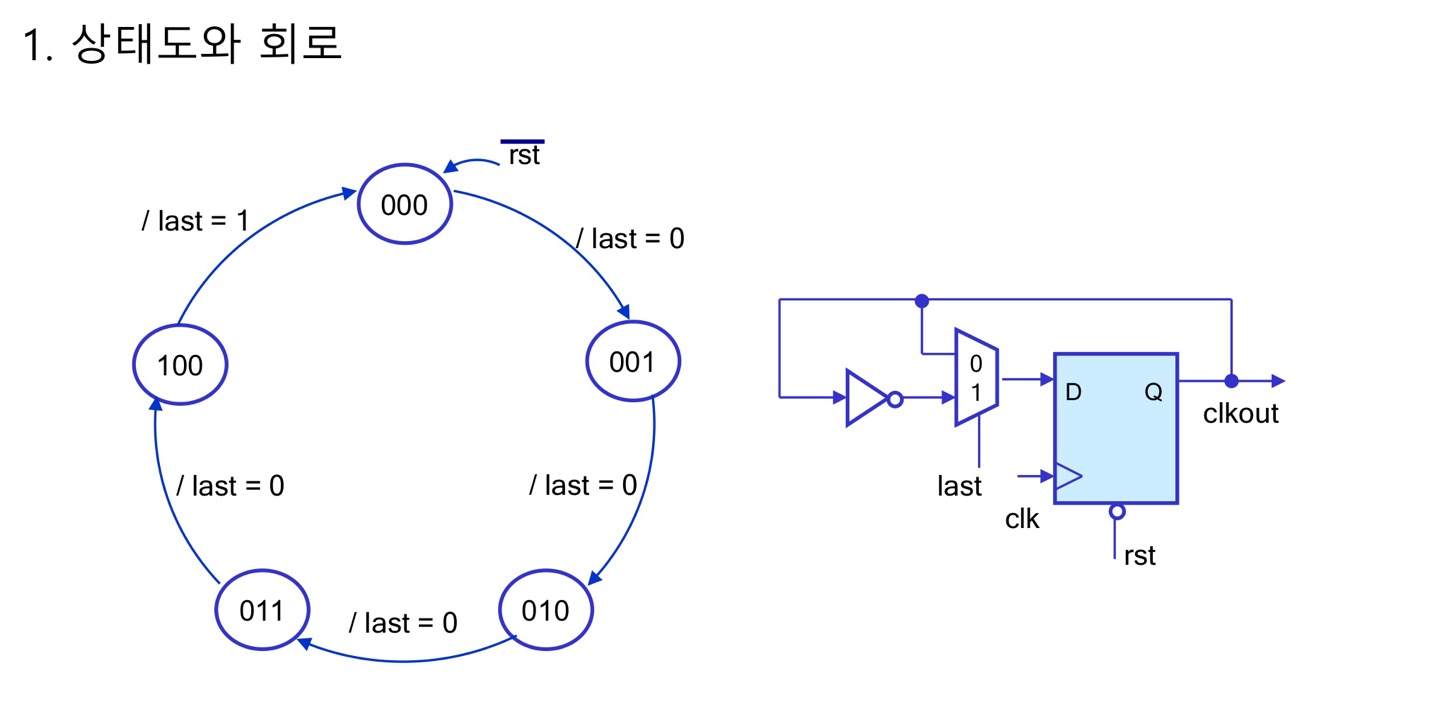

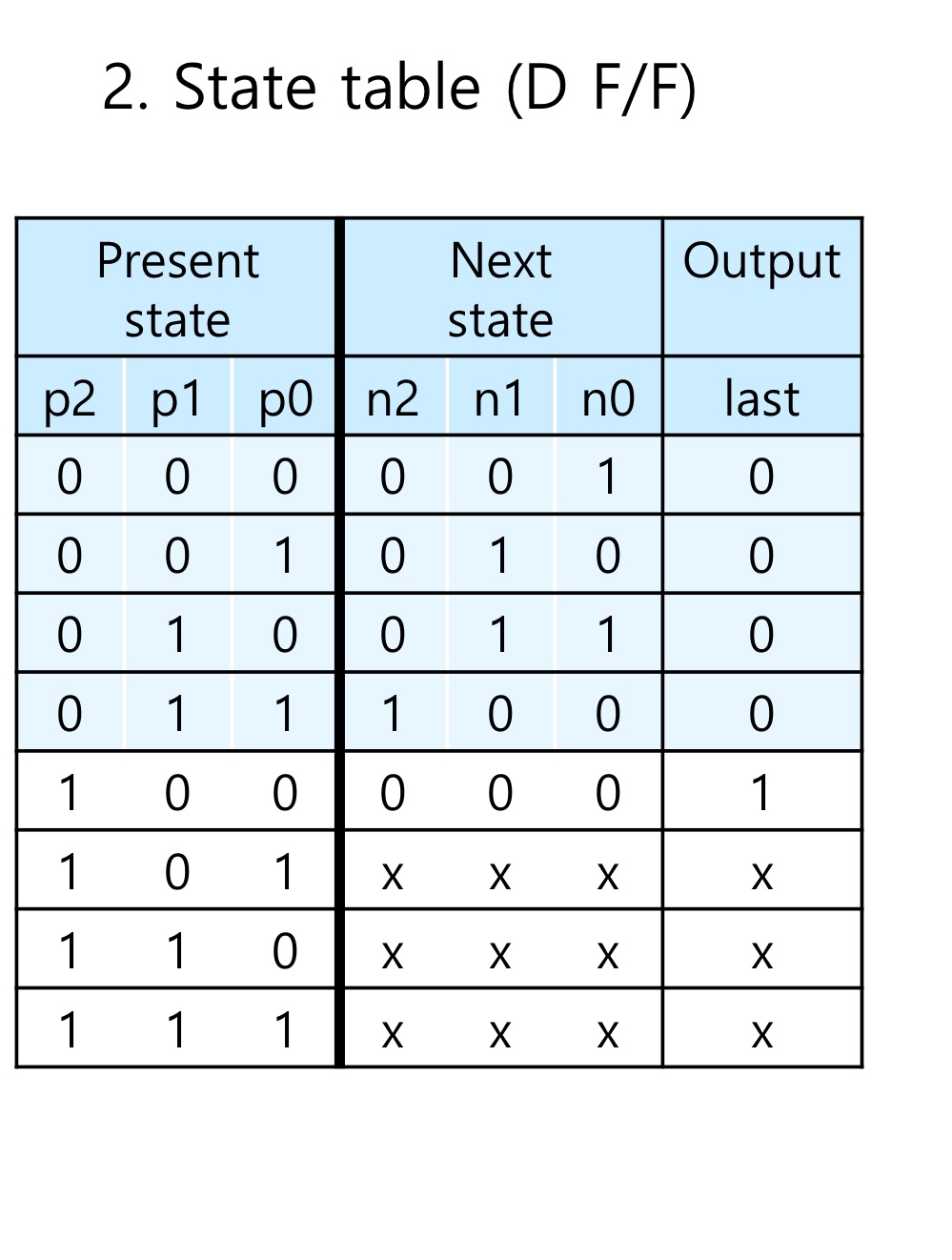

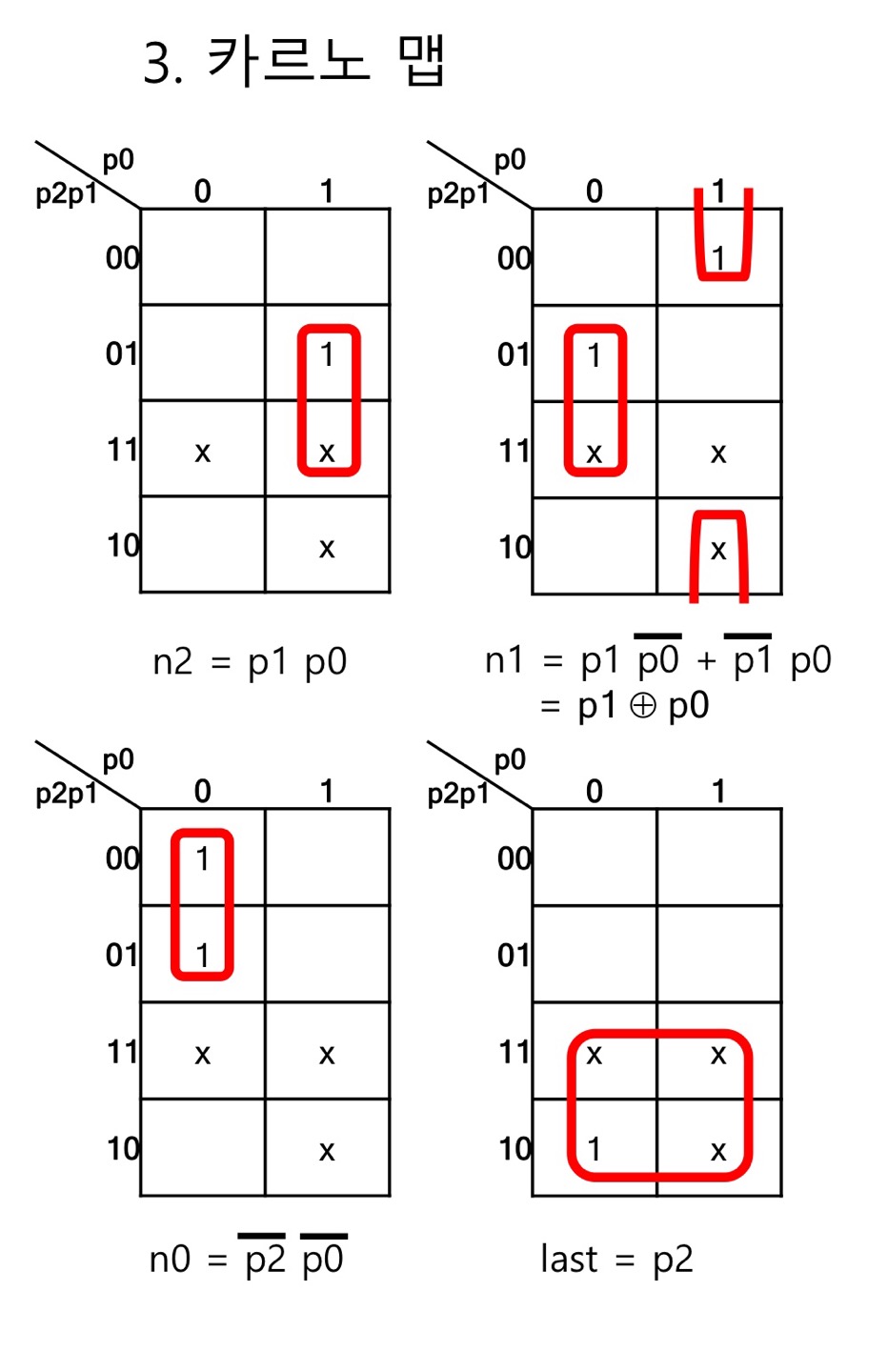

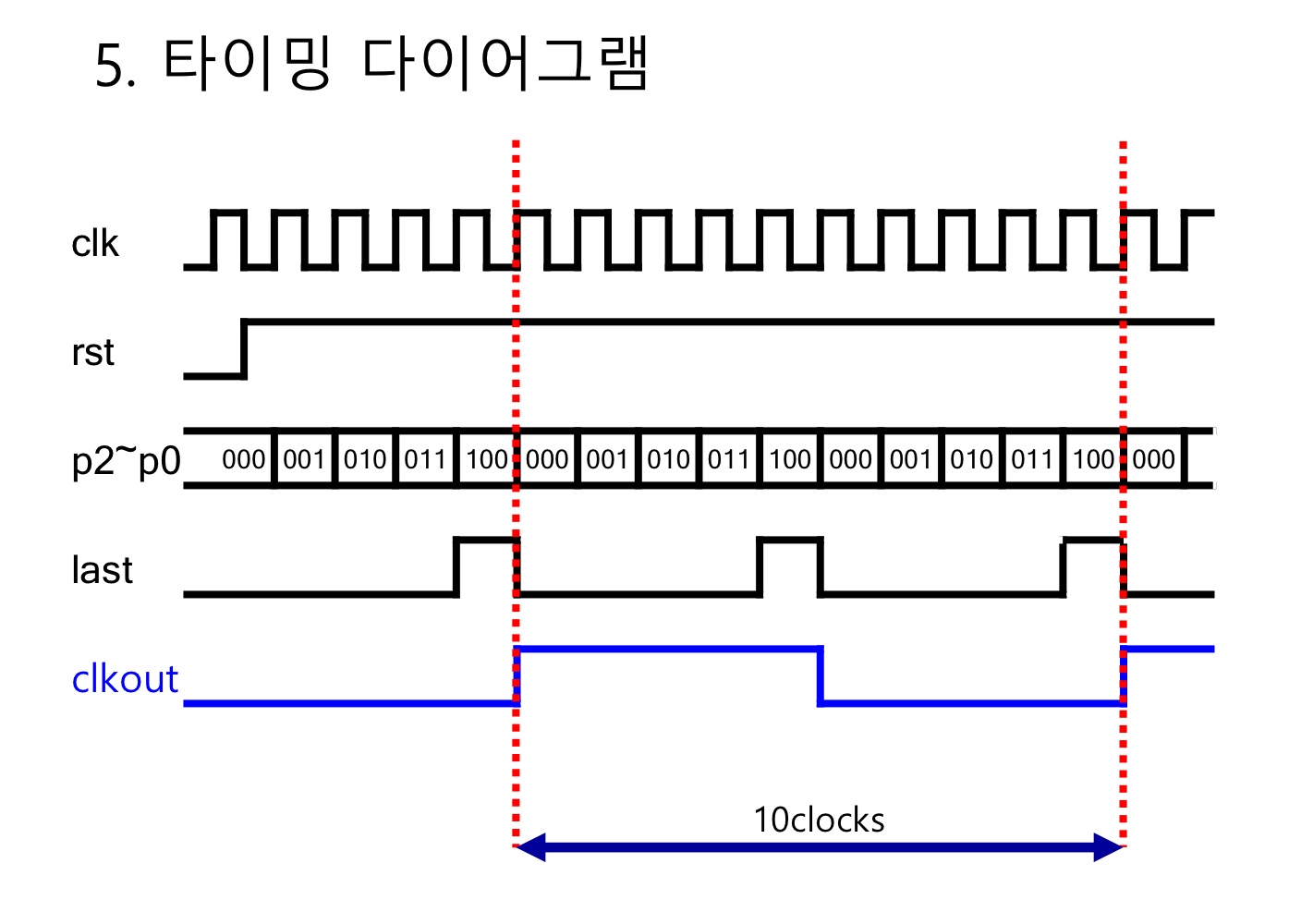

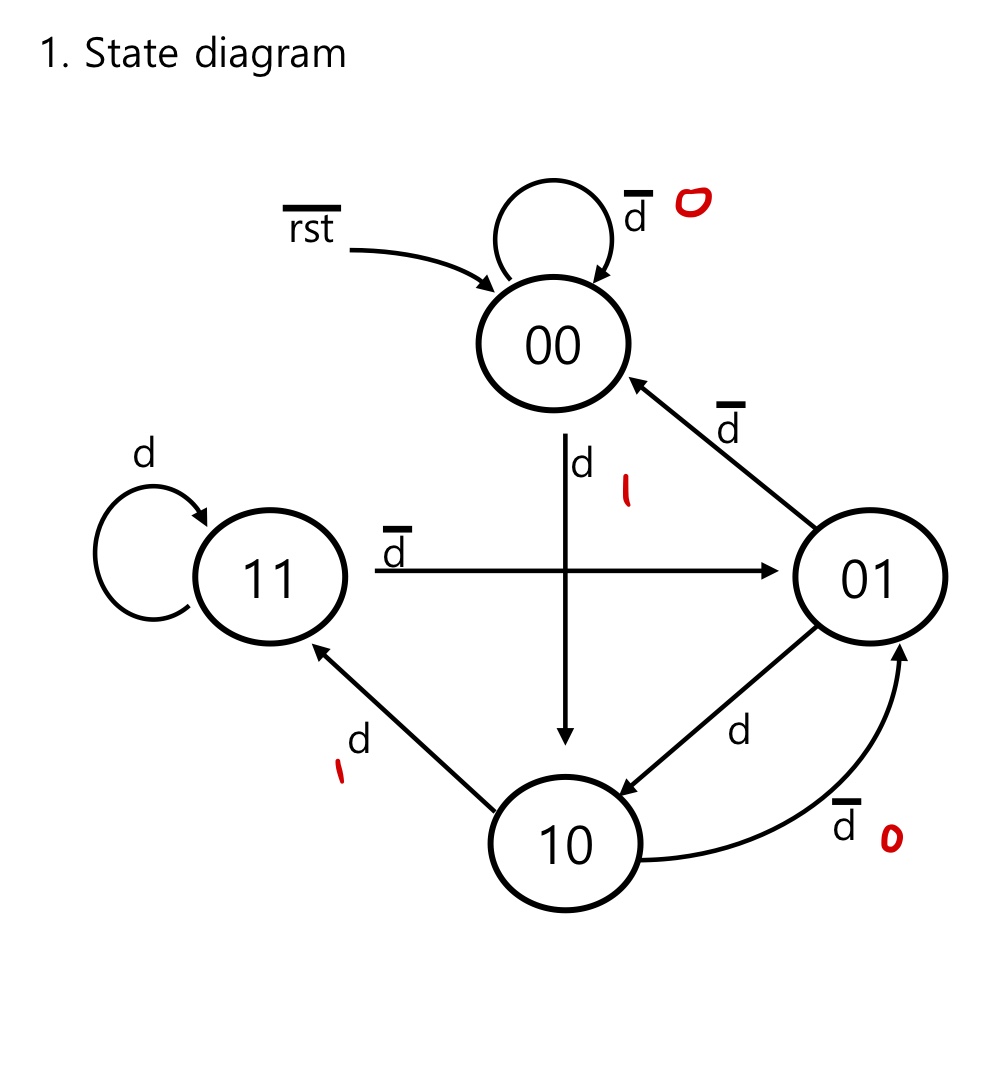

< 클럭 10분주기 >

- 000>001> -- > 100>000로 변하는 카운터

- 100이 되었을 때만 last=1이고 다음 클럭에서 clkout반전됨

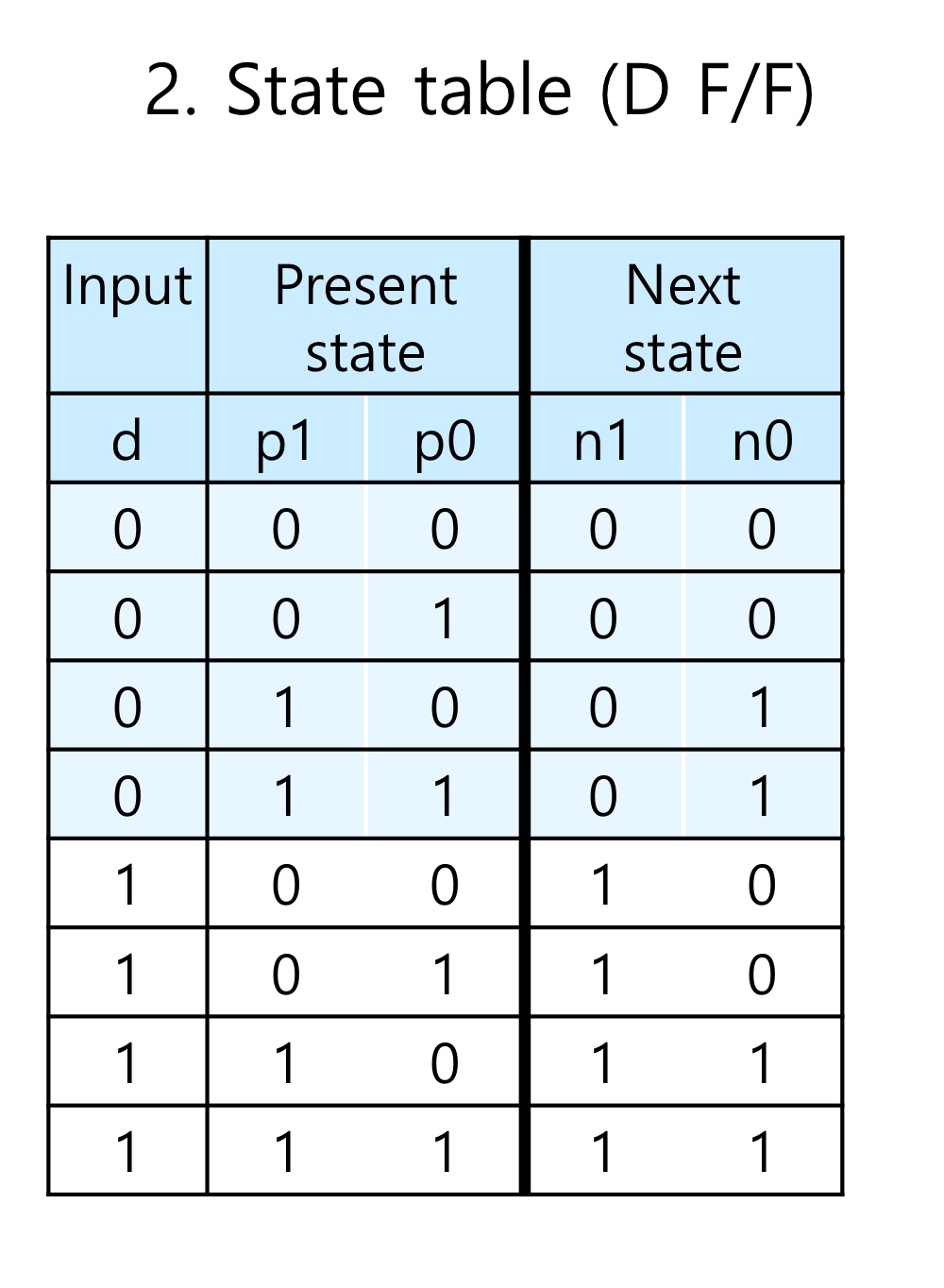

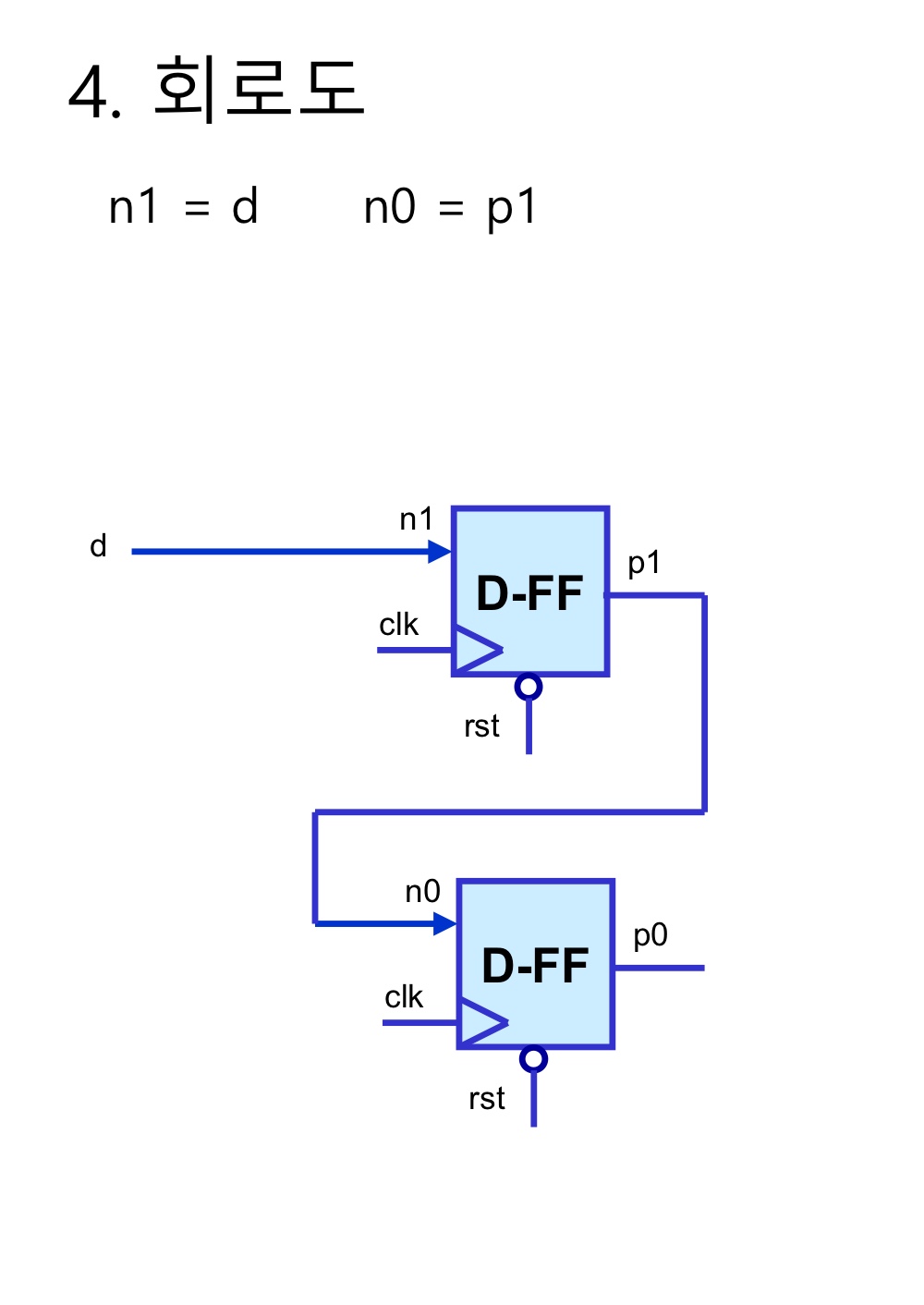

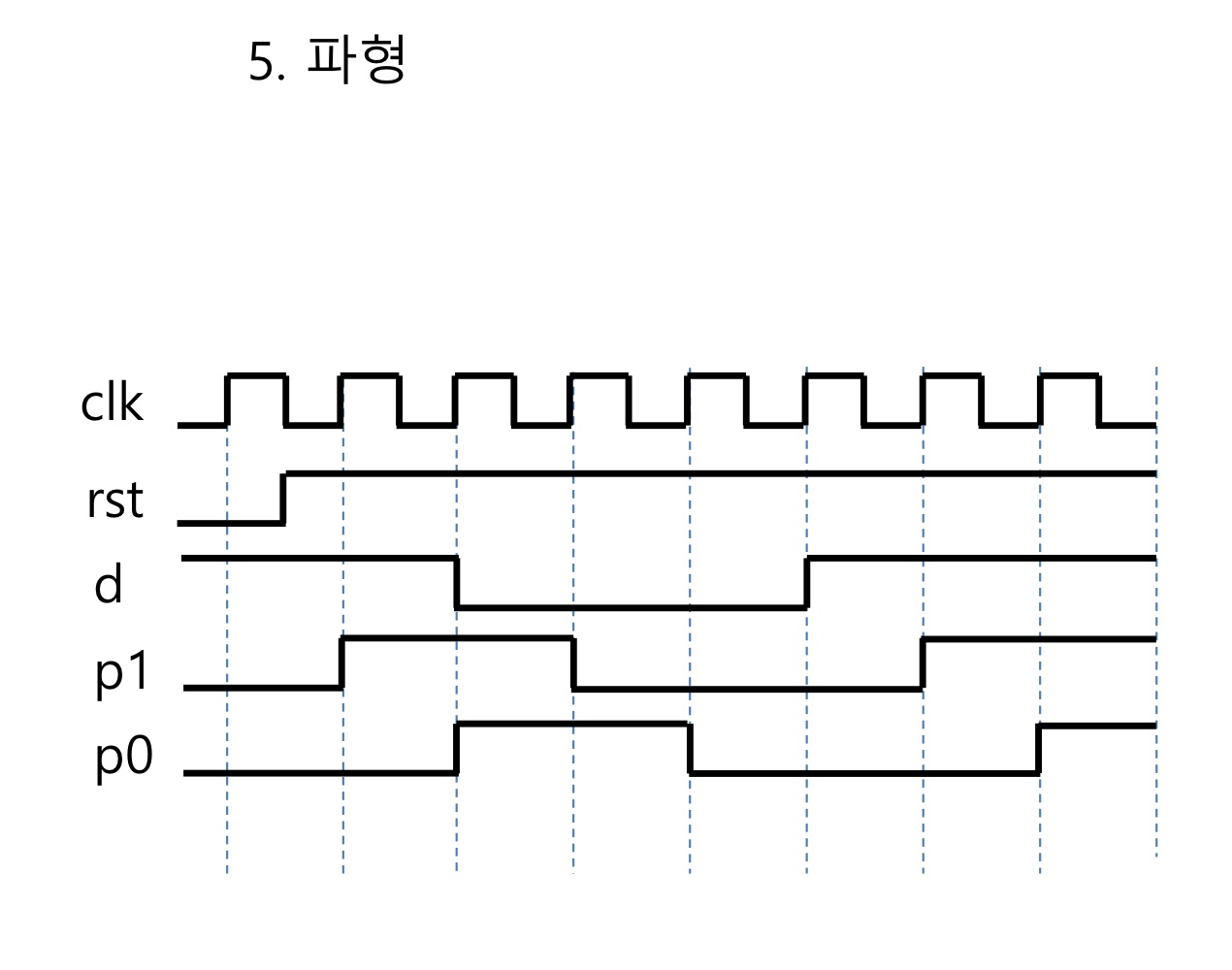

< FSM으로 만드는 시프트 레지스터 >

- 2비트 오른쪽 shift register

- 매 클럭마다 입력 d가 입력될 때마다 오른쪽으로 시프트

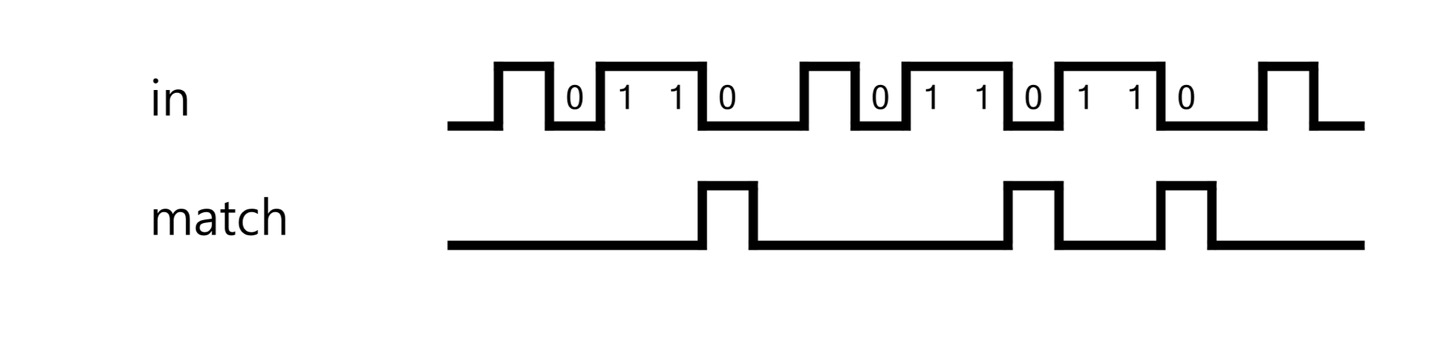

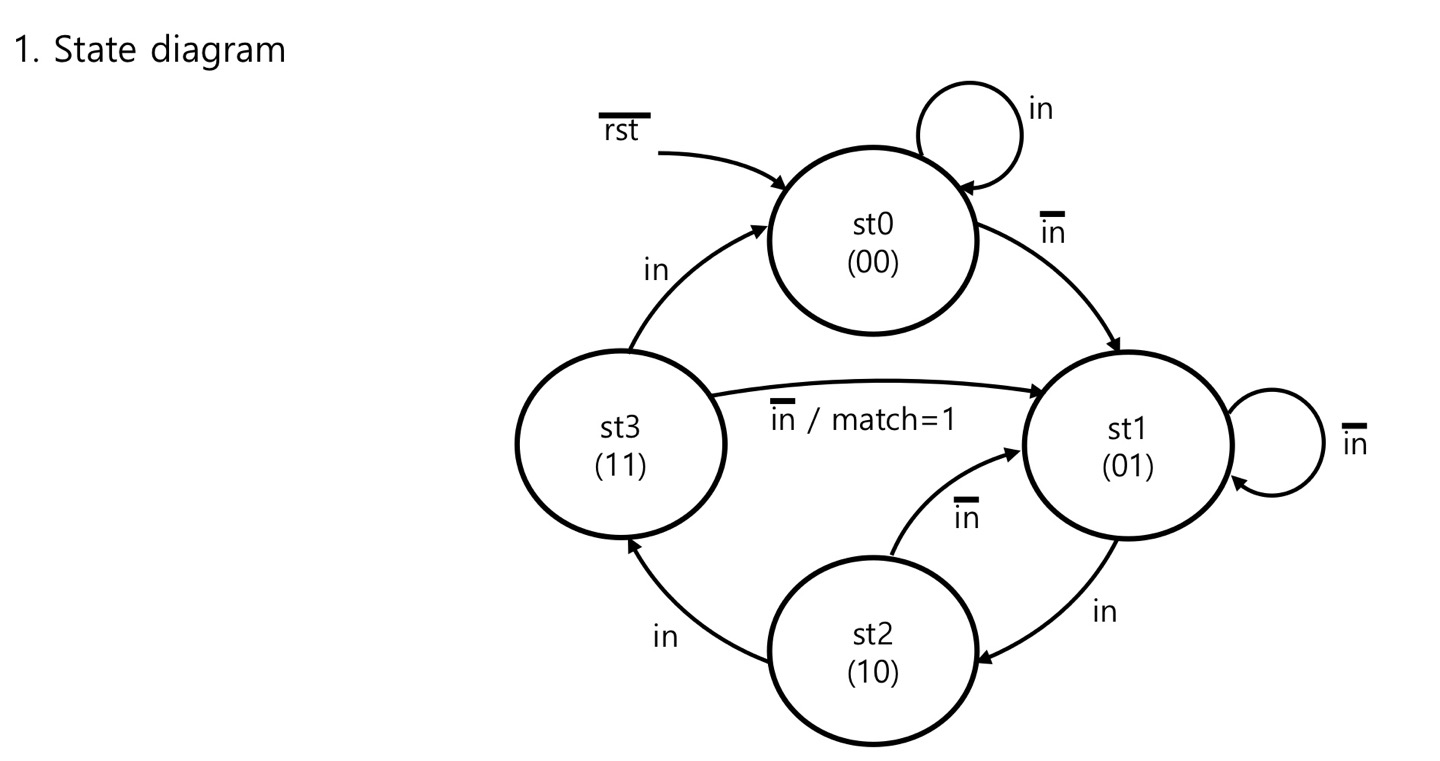

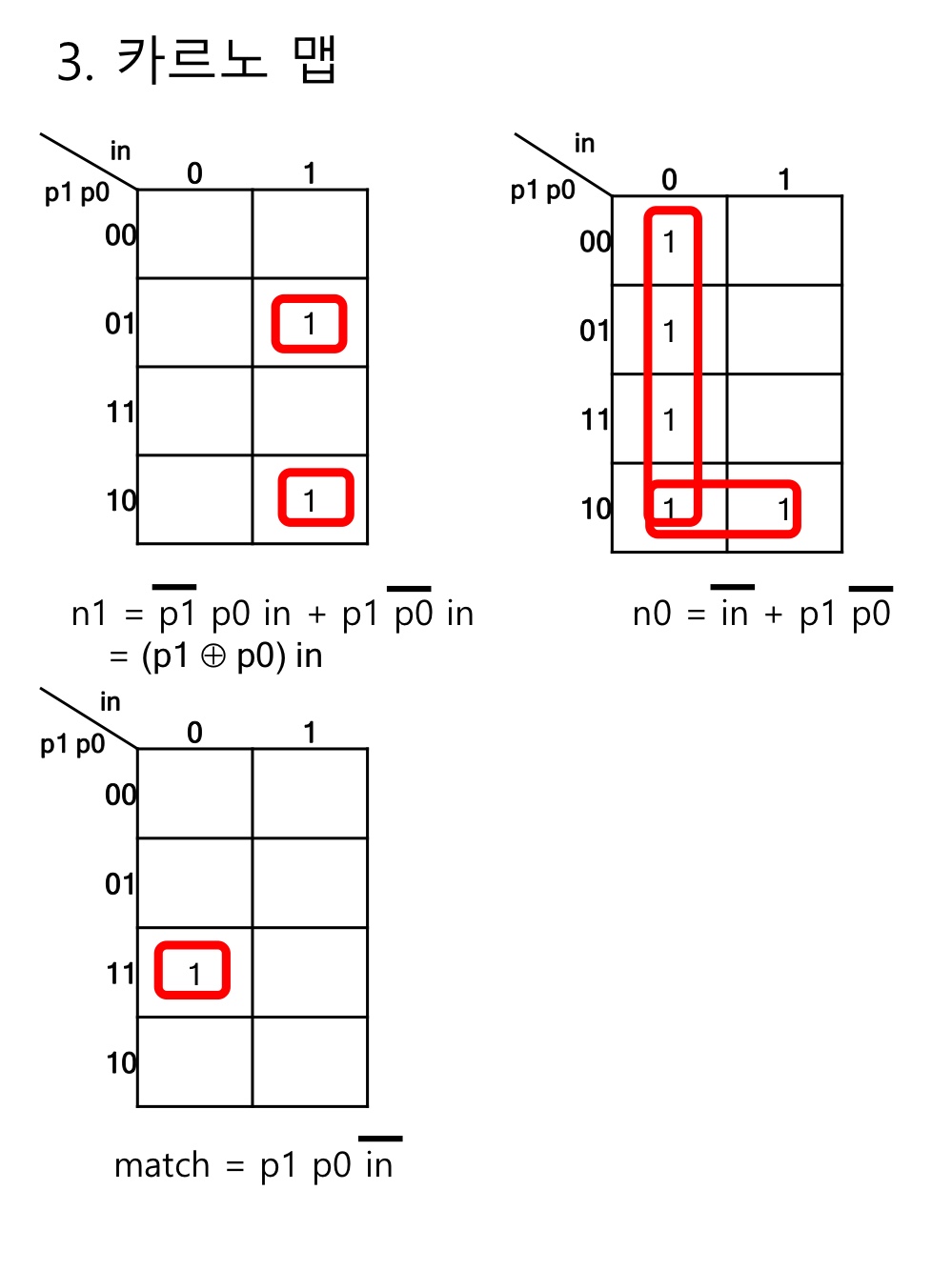

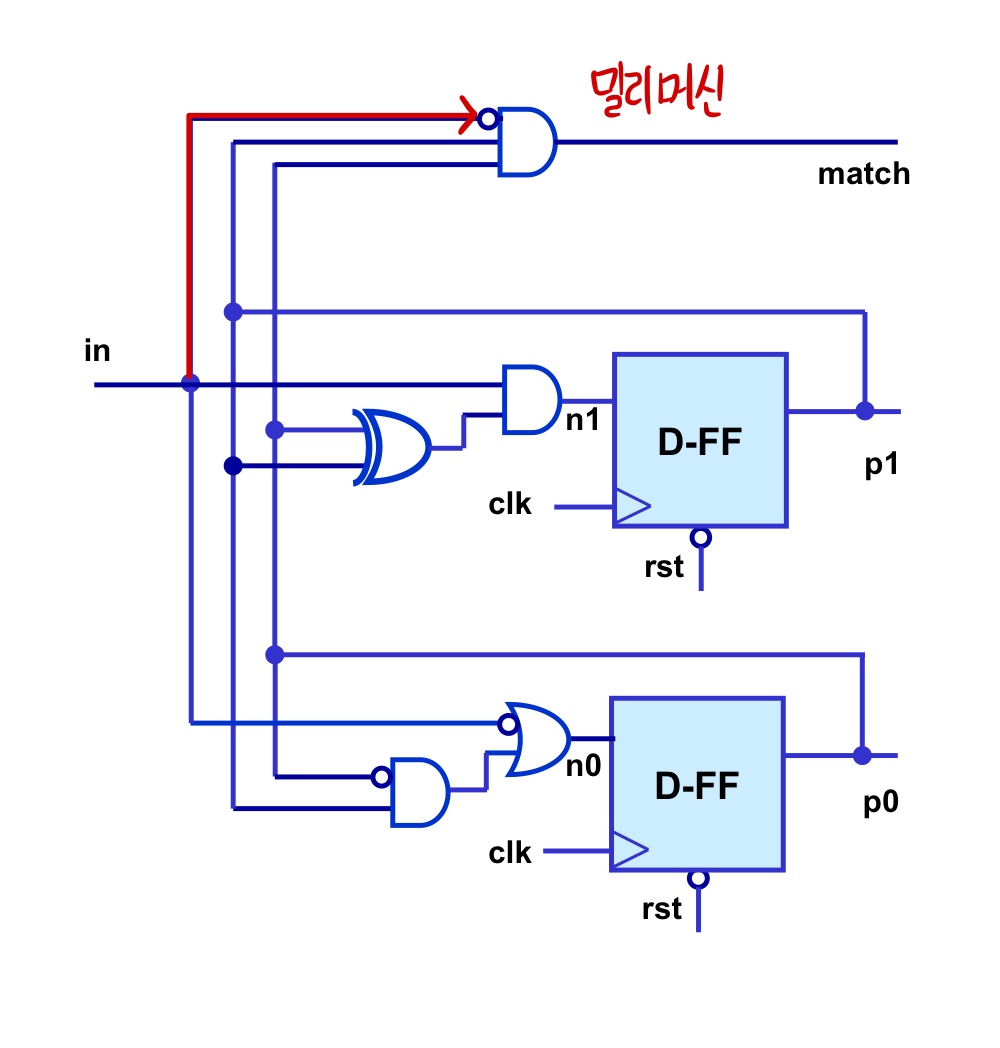

< FSM으로 만드는 number detector >

- 매 클럭마다 입력 in이 1비트씩 입력

- 일련의 숫자가 0110이 될때마다 출력 match신호는 1이 된다.

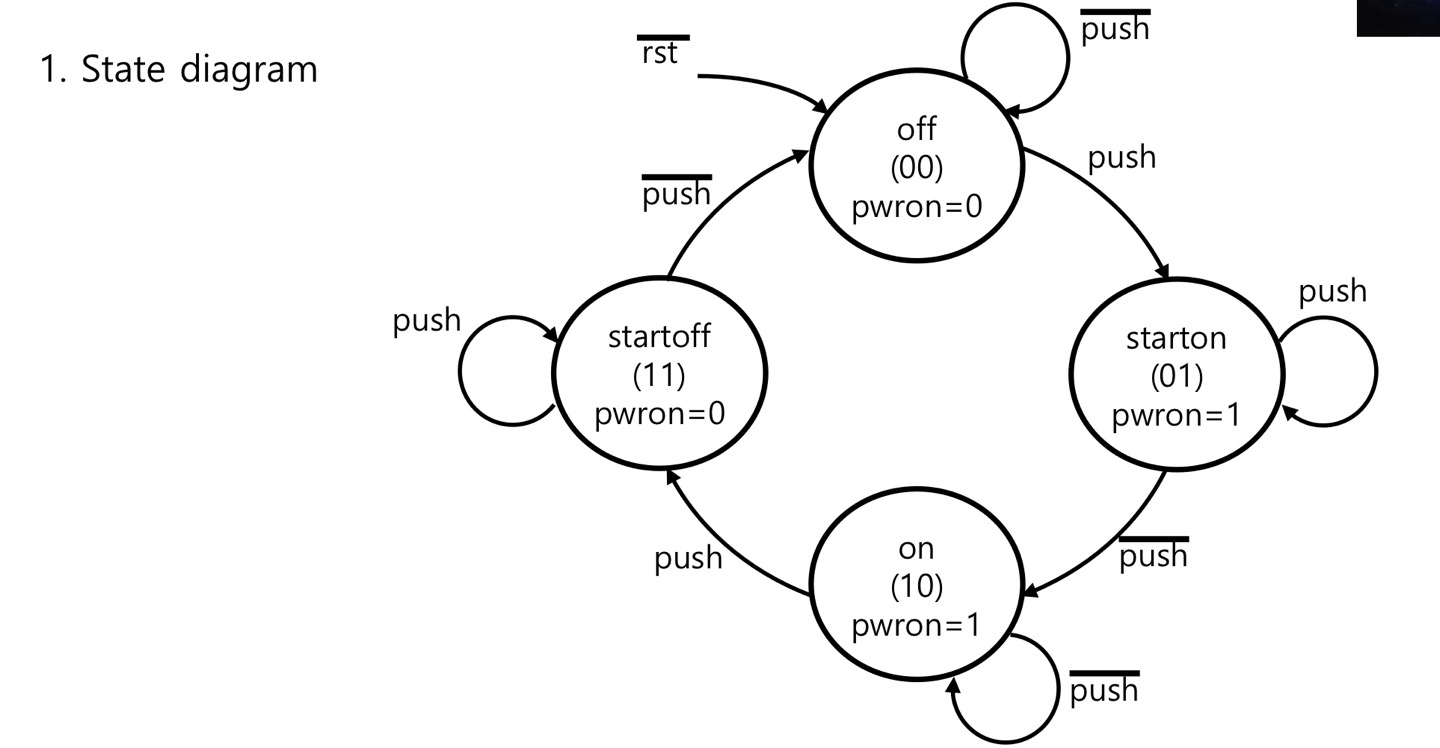

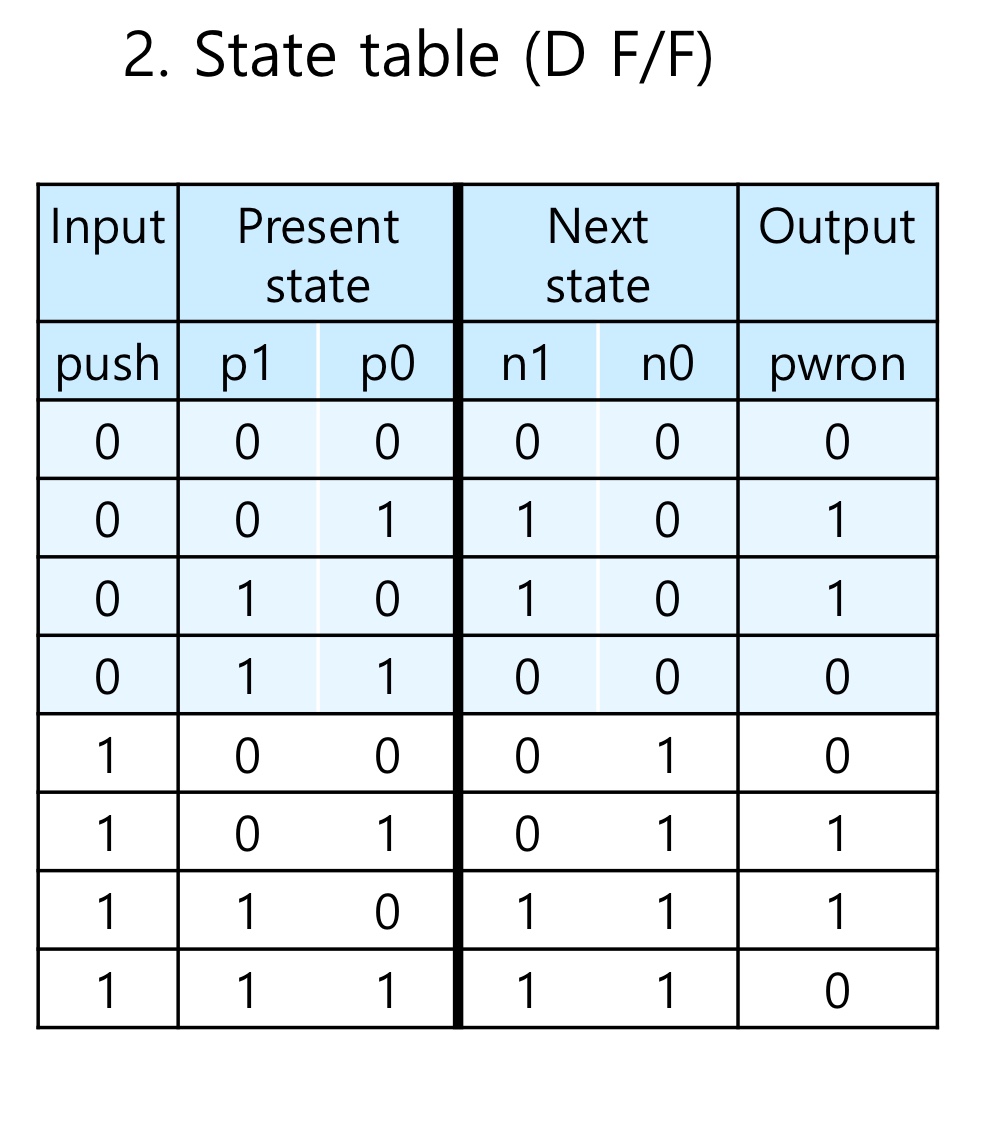

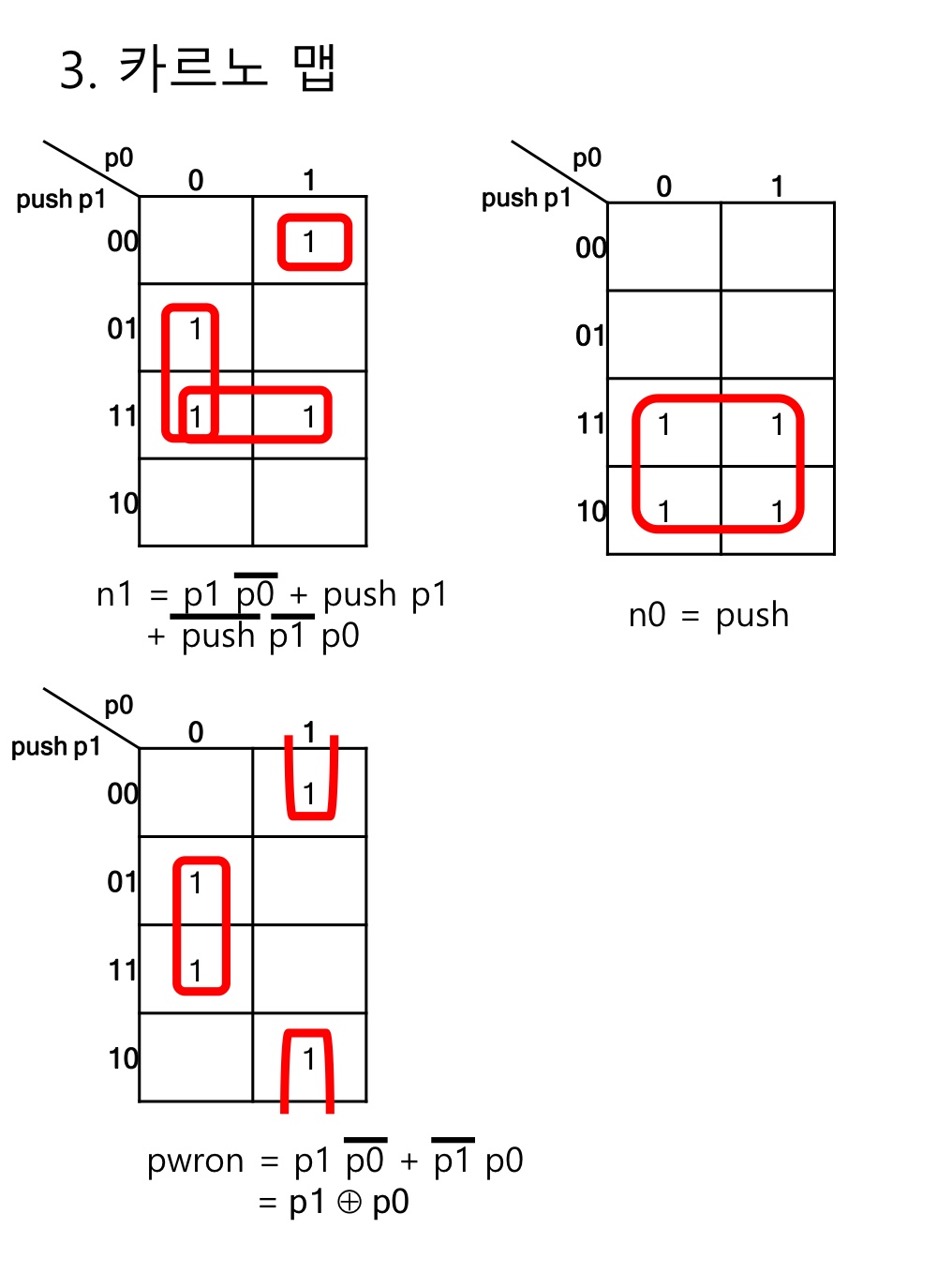

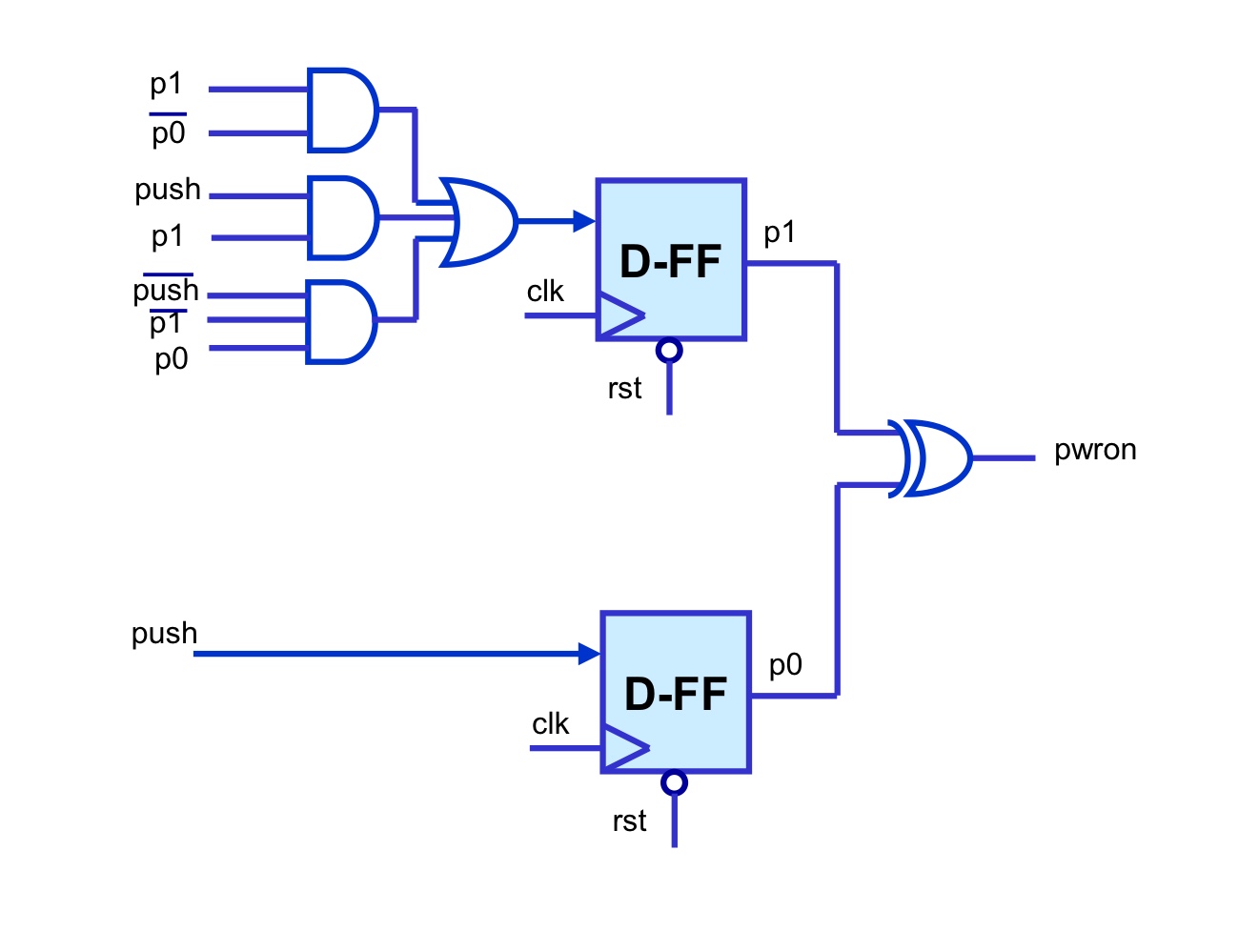

< 누름 전원 스위치 예제 >

- 같은 버튼으로 on또는 off할 수 있는 스위치

- 사람은 잠깐 누르지만 여러 번 누른것으로 인식되어 오동작을 할 수 있다.

- 이를 방지하기 위해 스위치를 누르 동작 뿐 아니라 때는 동작도 감지해야 된다.

- 입력 : push : 전원 스위치가 눌려 있는 경우 1

- 출력 : pwron : 동작 중일 경우 1

'Computer Architecture > 논리회로' 카테고리의 다른 글

| [17] CH9 레지스터 (0) | 2022.01.09 |

|---|---|

| [16] CH8 순차논리회로 < FSM+Counter 응용 설계 > (0) | 2022.01.09 |

| [14] CH8 순차논리회로 < 카운터 FSM 설계-2 > (0) | 2022.01.09 |

| [13] CH8 순차논리회로 < 카운터 FSM 설계 > (0) | 2022.01.09 |

| [12] CH8 순차논리회로 < 비동기-동기 카운터, FSM > (0) | 2022.01.09 |

@Return :: Return

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[17] CH9 레지스터](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FW20Xc%2FbtrqgcgvgMe%2FAAAAAAAAAAAAAAAAAAAAAOmZd9nMx6e5E3Ytx0XXxRMIQfpdvyRWXjXLdzlfrAGq%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DhjvIwg7p9qaFNf6ymZA183j5WCo%253D)

![[16] CH8 순차논리회로 < FSM+Counter 응용 설계 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fb4U0Mp%2Fbtrp7Hn2UEx%2FAAAAAAAAAAAAAAAAAAAAAGcrkKTPtGV2FPHQ_Bnz97XbFPmru9PJPKweQ3d8MPzm%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DNDgU%252BGBnBFZ7aRFXpov10P7CmAQ%253D)

![[14] CH8 순차논리회로 < 카운터 FSM 설계-2 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcSZJca%2Fbtrp6xte67u%2FAAAAAAAAAAAAAAAAAAAAAA3WkubiVvX6UwnmE5ve4iu5iExh190X0rRPqtrRG9eT%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3D62jaCUH4WT5R2JTMuxdRBFqJp5o%253D)

![[13] CH8 순차논리회로 < 카운터 FSM 설계 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbpKnYD%2Fbtrp8q0XhHR%2FAAAAAAAAAAAAAAAAAAAAAAmZXsgqbZq0aKjzTvXiWMMfGo5Q8lQScRZteusZVK21%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DqZyRLxz4GN9f70Fdf5x56OG7Og8%253D)