![[13] CH8 순차논리회로 < 카운터 FSM 설계 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbpKnYD%2Fbtrp8q0XhHR%2FAAAAAAAAAAAAAAAAAAAAAAmZXsgqbZq0aKjzTvXiWMMfGo5Q8lQScRZteusZVK21%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DqZyRLxz4GN9f70Fdf5x56OG7Og8%253D)

[13] CH8 순차논리회로 < 카운터 FSM 설계 >Computer Architecture/논리회로2022. 1. 9. 14:28

Table of Contents

< FSM의 설계 과정 >

1. 상태 다이어그램(state diagram)을 그린다.

2. 상태표(state table)을 작성한다.

3. 다음상태와 출력신호를 카르노맵으로 축약한다.

4. 회로도(schematic)를 작성한다.

5. 타이밍 다이어그램으로 동작을 확인한다.

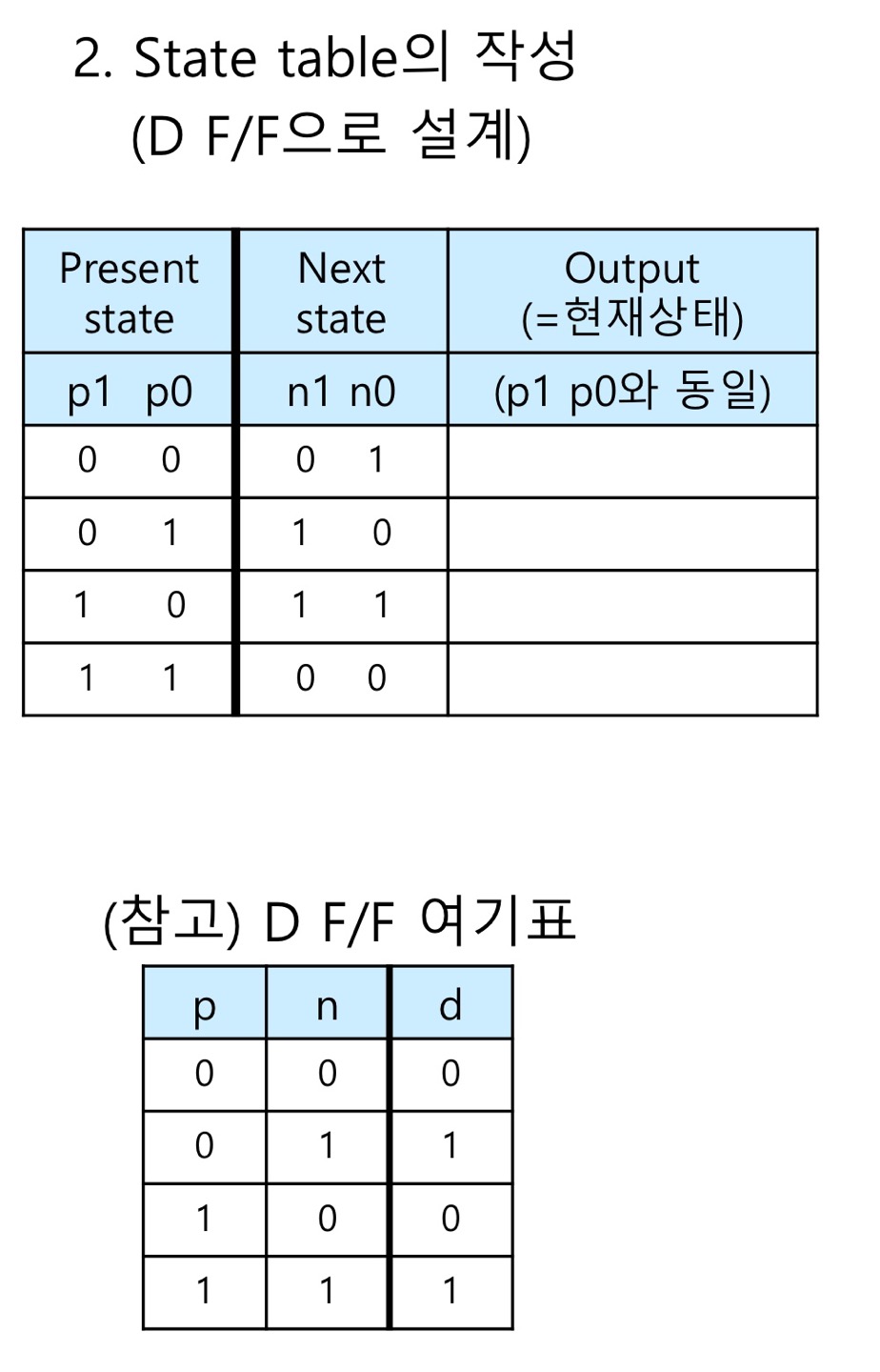

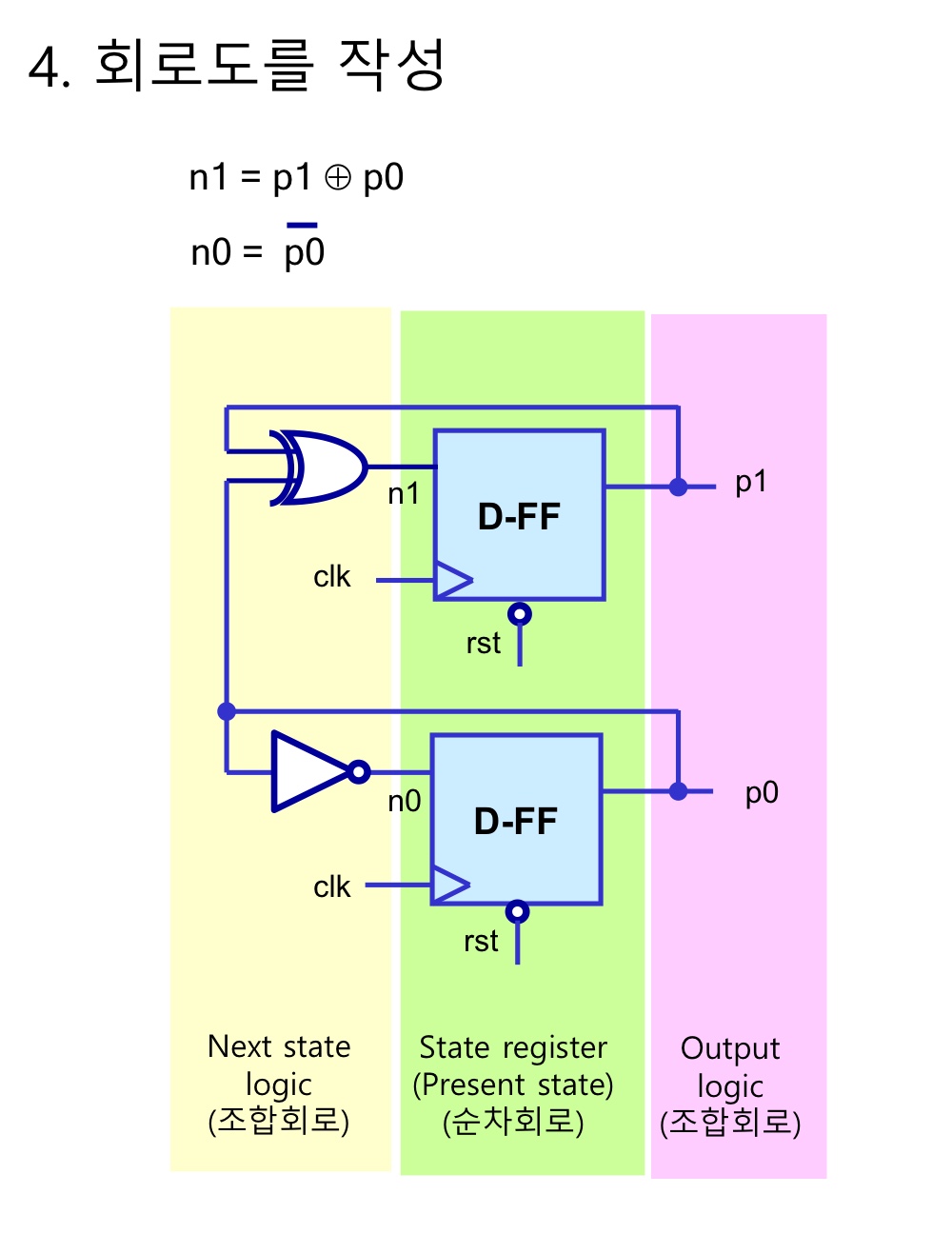

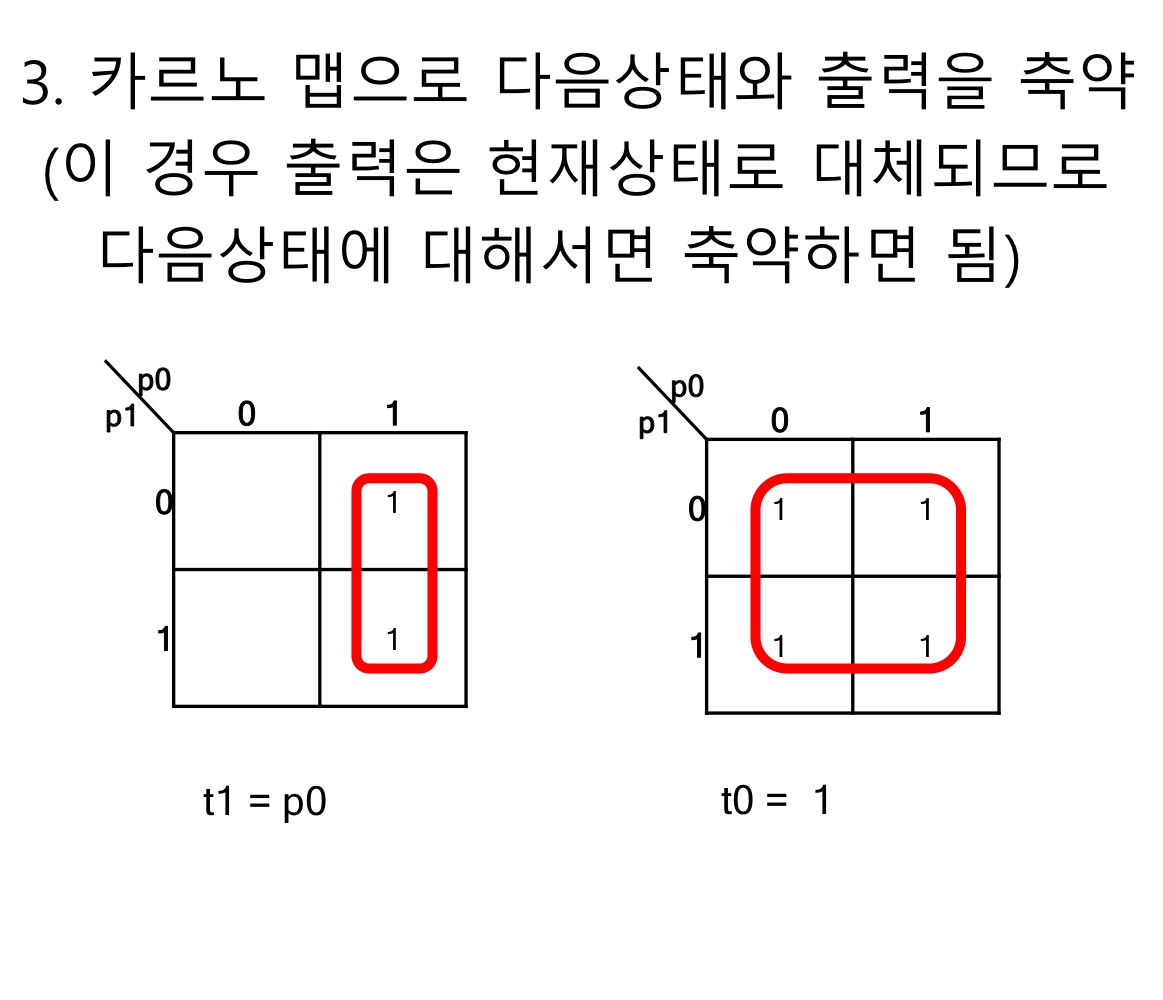

< 2비트 동기 카운터의 설계 >

- 00 > 01 > 10 > 11 > 00 > 01과 같이 값을 세는 카운터의 설계

1. State diagram의 작성

< D F/F으로 설계 >

< JK F/F으로 설계 >

< T F/F으로 설계 >

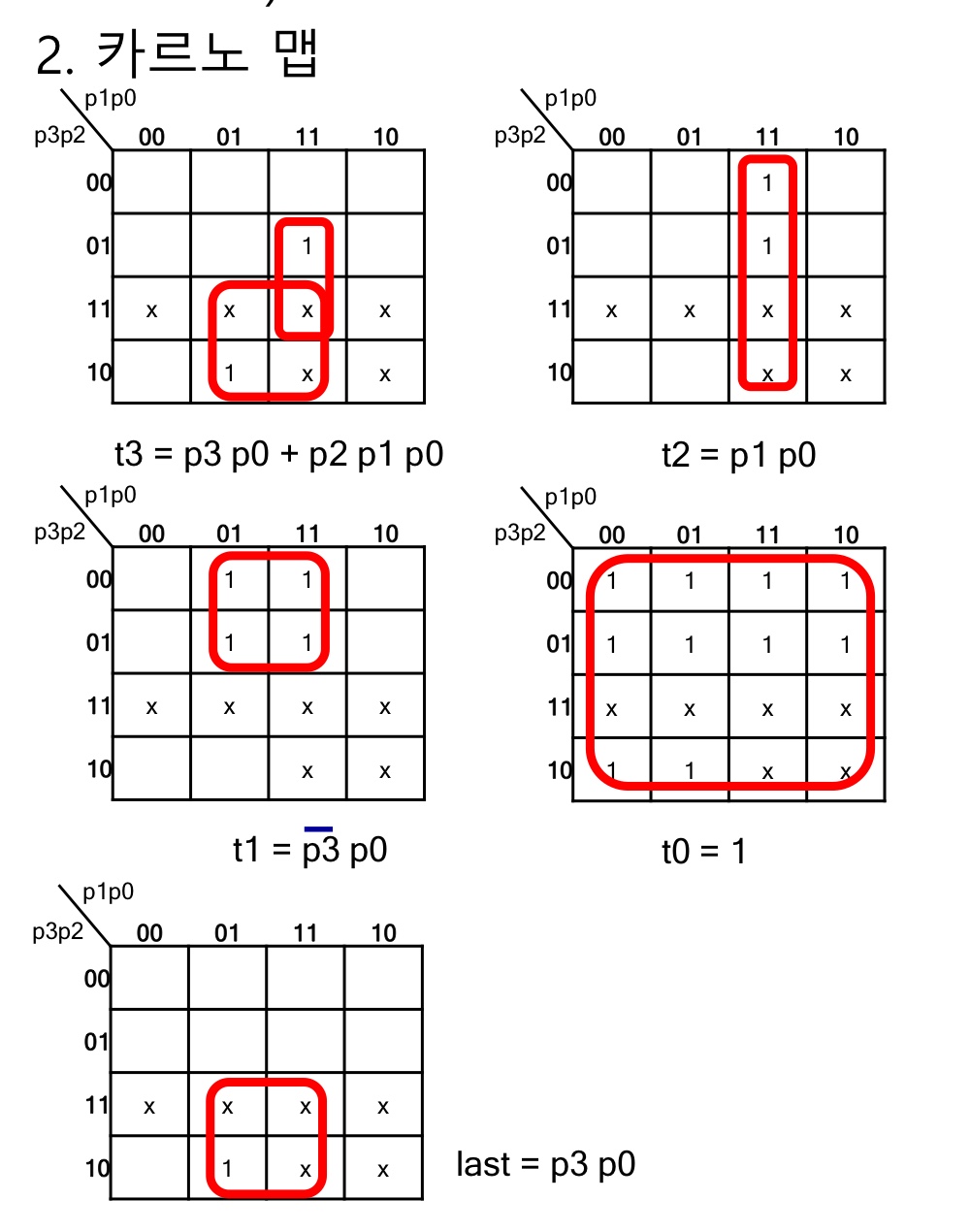

< 4비트 동기 Decade Counter(T F/F) >

- 0부터 9까지 그리고 다시 0부터 카운트 9일때는 last=1이 되는 카운터

'Computer Architecture > 논리회로' 카테고리의 다른 글

| [15] CH8 순차논리회로 < 카운터 FSM 설계-3 > (0) | 2022.01.09 |

|---|---|

| [14] CH8 순차논리회로 < 카운터 FSM 설계-2 > (0) | 2022.01.09 |

| [12] CH8 순차논리회로 < 비동기-동기 카운터, FSM > (0) | 2022.01.09 |

| [11] CH8 순차논리회로 < 플립플롭(Filp-Flops) > (0) | 2022.01.08 |

| [10] CH8 순차논리회로 < 래치(Latch) > (0) | 2022.01.06 |

@Return :: Return

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[15] CH8 순차논리회로 < 카운터 FSM 설계-3 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FesLF8c%2FbtrqaJMnq3K%2FAAAAAAAAAAAAAAAAAAAAAAvYg6H9zAXDZFi1gBkT0xrXpToeEGSZCc0xgF662ohc%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DH6XNkdfIVRLmEAn1v68ksrVb9P4%253D)

![[14] CH8 순차논리회로 < 카운터 FSM 설계-2 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcSZJca%2Fbtrp6xte67u%2FAAAAAAAAAAAAAAAAAAAAAA3WkubiVvX6UwnmE5ve4iu5iExh190X0rRPqtrRG9eT%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3D62jaCUH4WT5R2JTMuxdRBFqJp5o%253D)

![[12] CH8 순차논리회로 < 비동기-동기 카운터, FSM >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbfPFeS%2Fbtrp7RR04EQ%2FAAAAAAAAAAAAAAAAAAAAACUPmlB-vdPGJBOMkqSPxvvBqGHByVGxVOqHlhD-vZKv%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3Di%252BBbkp03GuXfHf29GJjHzLETdLE%253D)

![[11] CH8 순차논리회로 < 플립플롭(Filp-Flops) >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbSpzd8%2Fbtrp6RRRSqe%2FAAAAAAAAAAAAAAAAAAAAAE58-e6Su4EN3VmmPF2kqop2yThhFyKlmQuiAgM2Eb3a%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DxtiSIJCNX0rRgPvZ7Hzki6CarKM%253D)