![[DRAM] DRAM디바이스 컨트롤 로직](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fb9eK3G%2FbtrEcyruVXi%2FAAAAAAAAAAAAAAAAAAAAALg8hkofEHbPb1NlkuVkbKyqwX7hBYTbETBtBhtDVeRa%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DPw173d%252BVnuoTuh3nk%252FH2wi4B1Wg%253D)

Introduce

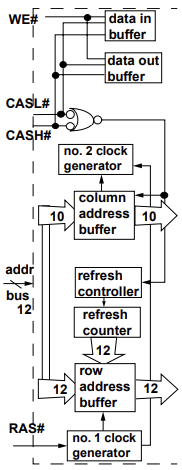

모든 DRAM 디바이스들은 DRAM 디바이스의 데이터의 onto, within, off이동을 지시하는 몇몇 기본적인 로직 컨트롤 회로를 가집니다. 필수적으로 몇몇 컨트롤 로직은 DRAM 디바이스상에 있어야 하며, 외부에 인가된 시그널을 받아들이고 컨트롤한 다음에 데이터의 이동을 지시하는 내부 컨트롤 시그널의 타이밍 시퀀스를 적절히 조율하는 역할을 합니다.

위는 FDM DRAM디바이스에서 데이터의 이동과 감지를 위한 시그널의 타이밍과 순서를 컨트롤하고 만들어내는 컨트롤 로직을 보여줍니다. FDM DRAM의 컨트롤 로직은 비동기로 외부의 컨트롤 시그널을 받아들이고, 내부의 컨트롤 시그널의 순서를 만들어냅니다. 필수적으로 3가지 시그널을 포함하는데, RAS, CAS, WE입니다. FDM DRAM은 16비트 데이터 버스를 가지고 있으며 분리된 CASL과 CASH 시그널의 사용은 DRAM디바이스가 각각 16비트 데이터 버스의 절반을 컨트롤하게 합니다.

FPM DRAM디바이스에서 컨트롤 로직과 외부 메모리 컨트롤러는 직접 데이터의 이동을 컨트롤합니다. 더욱이 FDM DRAM의 컨트롤러는 비동기 인터페이스이다. 이는 DRAM 디바이스가 잘 파이프라인 되지 않았고, 이전의 명령이 데이터의 이동을 끝낼 때까지 새로운 명령이 시작되지 않는다는 것을 의미합니다.

동기 vs 비동기

SDRAM(Synchronous DRAM), D-RDDRAM(Direct Rambus DRAM), DDR SDRAM(Dual Data Rate Synchronous DRAM)과 같은 최근의 DRAM디바이스들은 FDM DRAM보다 더 복잡한 컨트롤 로직을 포함합니다. 다음 그림은 SDRAM 디바이스의 컨트롤 로직을 나타낸 것입니다.

DRAM회로는 기본적으로 타이밍이 비동기식인 아날로그 회로입니다. DRAM 회로가 데이터를 sense amplifier를 통해 캐패시터에 저장하고 회수하는데 걸리는 과정은 상대적으로 긴 대기시간을 가집니다. 다른 DRAM제조업체의 다른 DRAM설계와 공정 변화는 각각의 타입과 설계의 DRAM디바이스가 다양한 타이밍 변수를 가지게 합니다. 비동기적인 특성과 DRAM 디바이스마다의 차이는 임시 메모리 저장장치로 DRAM 디바이스를 쓰는 컴퓨팅 플랫폼에 설계 복잡성을 가져다 줍니다. DRAM 산업에 의해 사용된 해결책은 DRAM 디바이스를 동기식 인터페이스로 변경하는 것입니다.

동기식 DRAM 디바이스 컨트롤 로직은 비동기식 인터페이스와 몇몇 중요한 다른 점이 있습니다. 클럭 시그널의 사소한 추가 외에도 주어진 명령하에서 동작에 경미한 차이를 보입니다. 동기식 DRAM 디바이스의 프로그래머블 변동성은 컨트롤 로직으로 내장된 모든 레지스터에 의해 컨트롤됩니다. 예를들어 SDRAM 디바이스는 column read command에 대해 다른 길이의 데이터 버스트와 다른 순서의 데이터를 출력하게 프로그램될 수 있다.

두번째 차이점은 동기식 로직은 자연스럽게 파이프라이닝을 지원하도록 설계되어 있어 DRAM 메모리 시스템이 수용할 수 있는 대역폭을 크게 늘어나게 하였습니다.

모드 레지스터 바탕의 프로그램화

DRAM 대바이스는 state machine에 의해 컨트롤되고, state machine의 동작은 명령 시그널의 입력값과 컨트롤 로직의 프로그래머블 모드 레지스터에 내장된 값에 의존합니다. 다음 그림은 SDRAM디바이스에서 mode register가 CAS 대기시간, 버스트 타입, 버스트 길이 등 3가지 면을 가지고 있는 것을 볼 수 있습니다. mode register의 CAS 대기 시간의 값에 따라 DRAM디바이스는 column read command를 인가한지 2cycle, 3cycle 후에 데이터를 출력시킵니다.

버스트 타입의 값은 SDRAM 디바이스가 어떤 순서로 데이터를 출력하는지를 결정하고, 버스트 길이는 SDRAM디바이스가 한 개의 column read command에 대해 메모리 컨트롤러로 출력시키는 column의 수를 결정합니다. SDRAM 느 1,2,4,8혹은 전체 row를 출력시킬 수 있게 프로그램되어 있습니다.

'Computer Architecture > 메모리 시스템' 카테고리의 다른 글

| [DRAM] DRAM 디바이스 종류 (0) | 2022.06.08 |

|---|---|

| [DRAM] 디코더와 리던던시 (0) | 2022.06.08 |

| [DRAM] RAM 어레이 구조 (0) | 2022.06.08 |

| [DRAM] DRAM 디바이스 조직과 저장 셀 (0) | 2022.06.08 |

| [DRAM] Differential Sense Amplifier(차동 증폭기) (0) | 2022.06.08 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[DRAM] DRAM 디바이스 종류](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FOAIUE%2FbtrEc4DnP5e%2FAAAAAAAAAAAAAAAAAAAAALOrGLMg1lnQjMhzNuHER1vexfcd0rkVhM6u6q36ZB_d%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3D87iNpqXaCnoOHqLp%252FHBnAf%252FyRf8%253D)

![[DRAM] 디코더와 리던던시](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2F1A4GY%2FbtrEeYvJ4Qd%2FAAAAAAAAAAAAAAAAAAAAANabLNNx9fIDxayDR5OxsqGcUOCBIHc4Y9da-p5xCEq7%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3Dtgx%252FxUg1eAe7i2zTyWd3g6GGsiU%253D)

![[DRAM] RAM 어레이 구조](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcHeqsJ%2FbtrEdSiiLrD%2FAAAAAAAAAAAAAAAAAAAAAP1KF3EbMJsp_0s1RD4Q9qwEEtqqkRur30lLsrTgF4dy%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DdwPIHRdRXj6zgZFhqX6r01Z6Zr4%253D)

![[DRAM] DRAM 디바이스 조직과 저장 셀](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FKEd5E%2FbtrEbEyTkMa%2FAAAAAAAAAAAAAAAAAAAAAPerp41wuA1RGoypJXj_UyUx8blCUEQtYv-bpeGPba6c%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3D1GOsiZC3uPpfIX4l68uGHwYMfwQ%253D)