![[11] PHY Interface for the PCI Express 간단히 알아보기](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FejVgVs%2FbtsI1FZZYR7%2FAAAAAAAAAAAAAAAAAAAAAOmQJJt9K0BlmhYgB4fzX4UQklIhjqP24V189vY1xv8U%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DjDhUYkB%252FdyCQyaUhYmBbQUTPCWc%253D)

이 글은 제가 PCIe를 공부하면서 겪은 시행착오를 바탕으로 정리한 글입니다. PCIe를 처음 접하는 분들에게 좋은 길라잡이가 되었으면 합니다.

이전 글)

[10] PCIe - Physical Layer (LTSSM) - 2

returnclass.tistory.com

PIPE

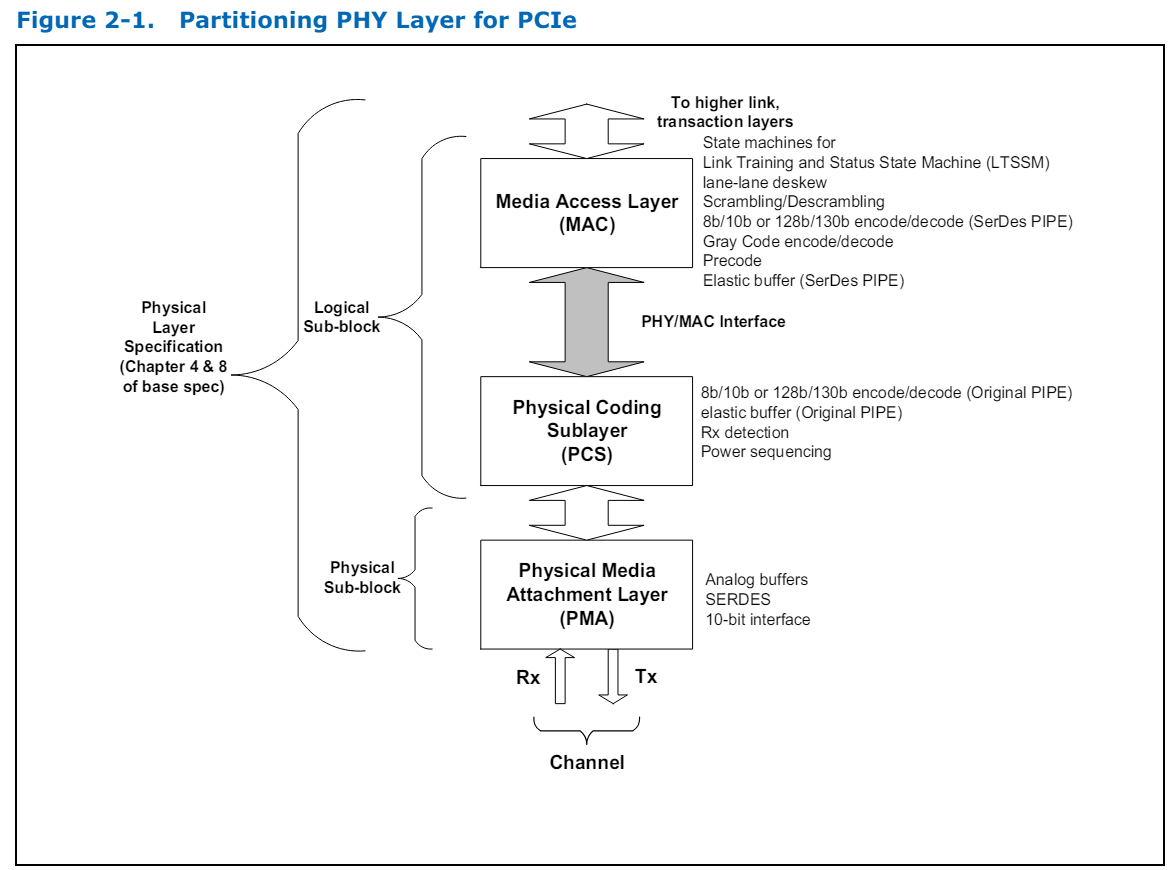

PIPE(PHY Interface for the PCI Express) 인터페이스는 인텔이 개발한 표준 인터페이스로, PCI Express(PCIe)의 물리 계층(PHY)과 프로토콜 계층 간의 상호작용을 최적화하기 위해 설계되었습니다. 이 인터페이스는 데이터 전송의 효율성과 호환성을 극대화하여, 다양한 제조업체들이 PCIe 호환 제품을 빠르고 쉽게 개발할 수 있도록 돕습니다. PIPE는 8b/10b 또는 128b/130b encoding, scrambling/descrambling 같은 작업을 표준화된 방식으로 처리하며, 물리 계층의 안정적인 동작을 보장합니다. 이를 통해 PIPE 인터페이스는 PCIe의 고속 데이터 전송 능력을 지원하고, 전체 시스템의 성능을 향상시키는 중요한 역할을 합니다.

Original PIPE vs SerDes PIPE

PIPE 인터페이스에는 크게 두 가지 버전이 있습니다. 이 두가지 버전의 차이는 기존의 PCIe의 physical layer의 component 중에서 어떤 부분까지 MAC component로 둘지에 있습니다. Original PIPE에서는 scrambler와 descrambler까지만 MAC의 component로 삼았으며, 나머지 encoder/decoder, elastic buffer와 같은 component는 PHY에 속해있었습니다. 하지만 SerDes PIPE에서는 encoder/decoder와 elastic buffer역시 MAC의 component로 편입되었으며, 그로인해 PHY의 component는 Serializer/De-serializer, Tx/Rx만 남게 되었습니다. PIPE 스펙에 따르면 SerDes PIPE가 권장사항이기에, 앞으로의 설명은 SerDes PIPE 기준으로 하겠습니다.

PHY/MAC Interface

PCLK와 같이 모든 lane이 공유하는 신호들을 제외하고, 나머지 신호들에 대해 각 interface는 lane당 있습니다.

Reference)

- PHY Interface for the PCI Express*, SATA, USB 3.2, DisplayPort*, and USB4* Architectures. Revision 6.2.1

'Interface Standards > PCIe' 카테고리의 다른 글

| [12] ATS (Address Translation Service) (0) | 2025.01.13 |

|---|---|

| [10] PCIe - Physical Layer (LTSSM) - 2 (0) | 2024.06.24 |

| [9] PCIe - Physical Layer (LTSSM) - 1 (0) | 2024.05.28 |

| [8] PCIe - Physical Layer (PCIe Gen3 ~) (0) | 2024.05.27 |

| [7] PCIe - Physical Layer (PCIe Gen1 & Gen2) - Receive Logic (0) | 2024.05.26 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[12] ATS (Address Translation Service)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdaolaK%2FbtsLNxpS0PM%2FAAAAAAAAAAAAAAAAAAAAAMbDX-XX2q4w5dAH2lk0L5lhOdSHVCZq6YWZ_yL94vrH%2Ftfile.dat%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DlTp8wmZwMMVSAQQjjjG2FBz%252F%252FJk%253D)

![[10] PCIe - Physical Layer (LTSSM) - 2](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2Fbk0lNb%2FbtsIbrUR2RL%2FAAAAAAAAAAAAAAAAAAAAAHmv2BIWvjyWHVtbiKK-7gziHRx6KomyGU4W7z7JE0nH%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3DEWYRFZmA23eeOIUtZr5lmX7mFUs%253D)

![[9] PCIe - Physical Layer (LTSSM) - 1](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FdcDFdw%2FbtsHF1vNnY2%2FAAAAAAAAAAAAAAAAAAAAAO4l3lophQk2kagz8bhtmDMEV0EYm-4aPno9SdEFb2WZ%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3D1iUZqhB%252F5vbnEXPMkaO2241Sdak%253D)

![[8] PCIe - Physical Layer (PCIe Gen3 ~)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2F1r2nf%2FbtsHCqJNKUJ%2FAAAAAAAAAAAAAAAAAAAAAAvemdzUNT-ThbkSmV_EzSHKnwaL18bGgEVxXEZbtaO-%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1764514799%26allow_ip%3D%26allow_referer%3D%26signature%3D05dDcLr%252FyJxrsemxqm77mKd9W1U%253D)