![[12] CH8 순차논리회로 < 비동기-동기 카운터, FSM >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbfPFeS%2Fbtrp7RR04EQ%2FAAAAAAAAAAAAAAAAAAAAACUPmlB-vdPGJBOMkqSPxvvBqGHByVGxVOqHlhD-vZKv%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3Di%252BBbkp03GuXfHf29GJjHzLETdLE%253D)

< Asynchronous vs Synchronous >

Synchronous(동기) 회로

- 모든 F/F이 동시에 동작. 즉, clock의 rising edge에 동시 동작한다.

- 모든 F/F의 clk단자에 같은 clock 신호가 입력된다.

- 설계가 쉽다.

Asynchronous(비동기) 회로

- 모든 F/F이 동시에 동작하지 않는다.

- 모든 F/F의 clk단자에 같은 clock신호가 입력되지 않는다.

- 설계가 어렵다.

- 경우에 따라서는 속도 향상 효과가 있다.

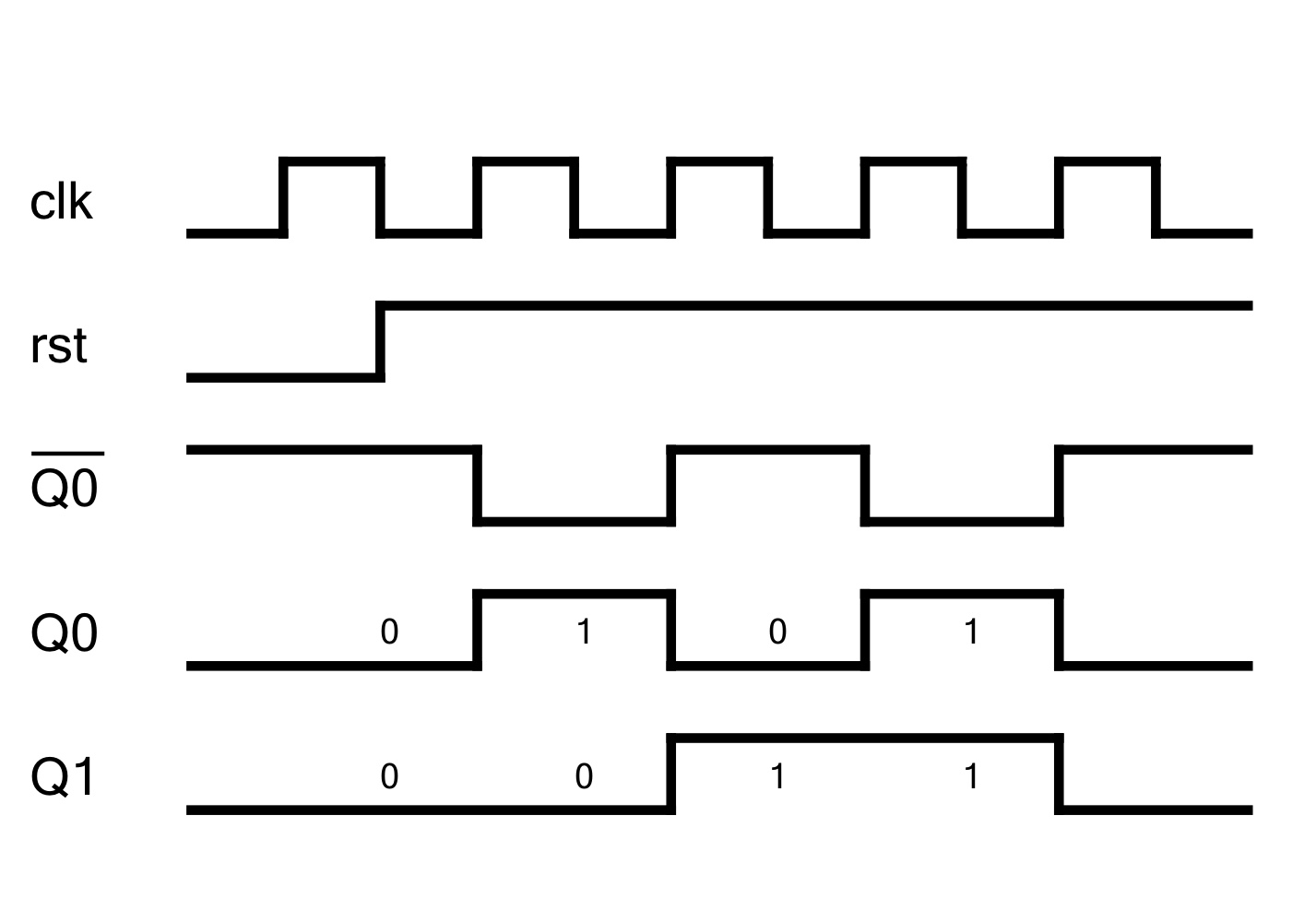

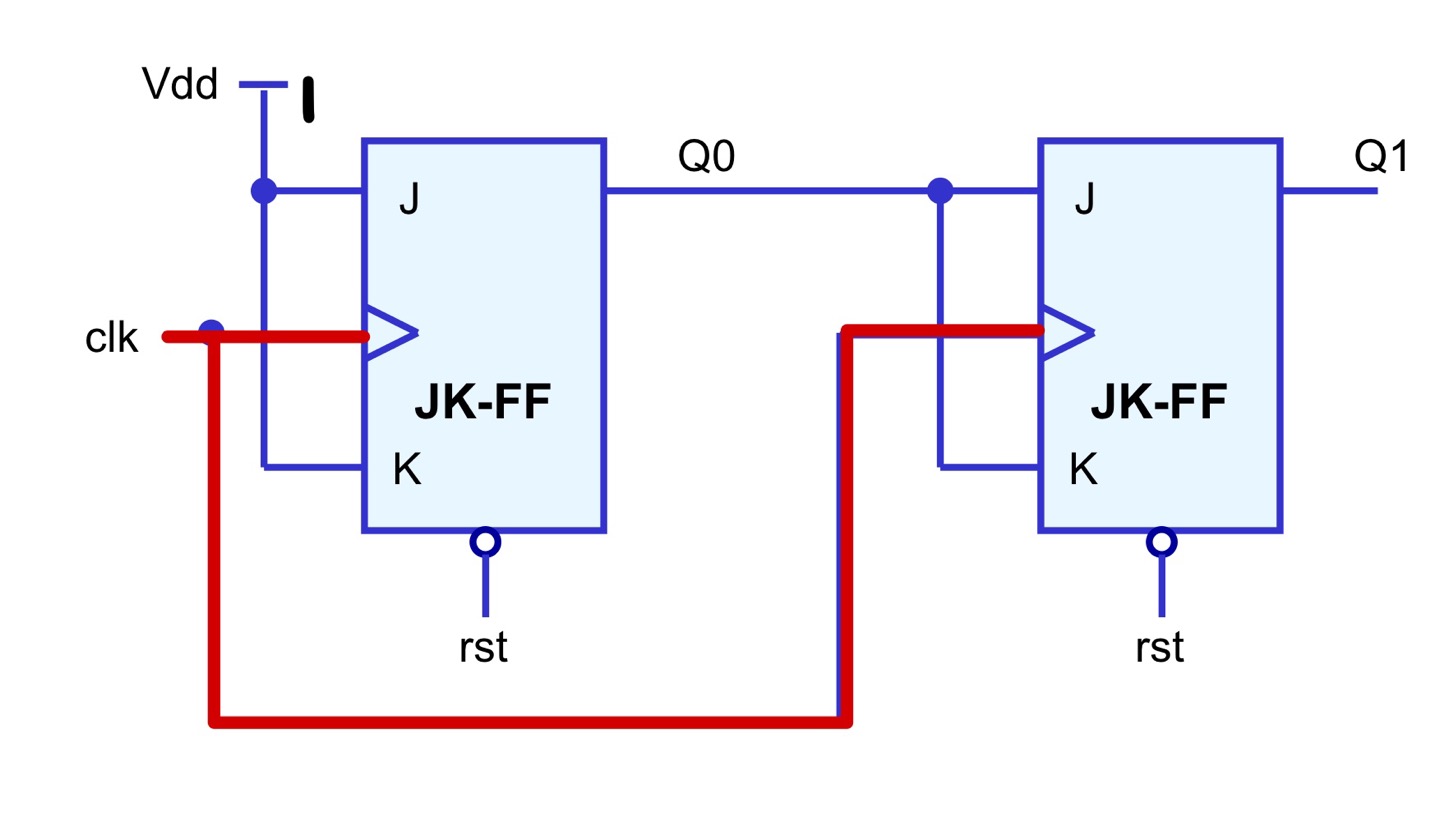

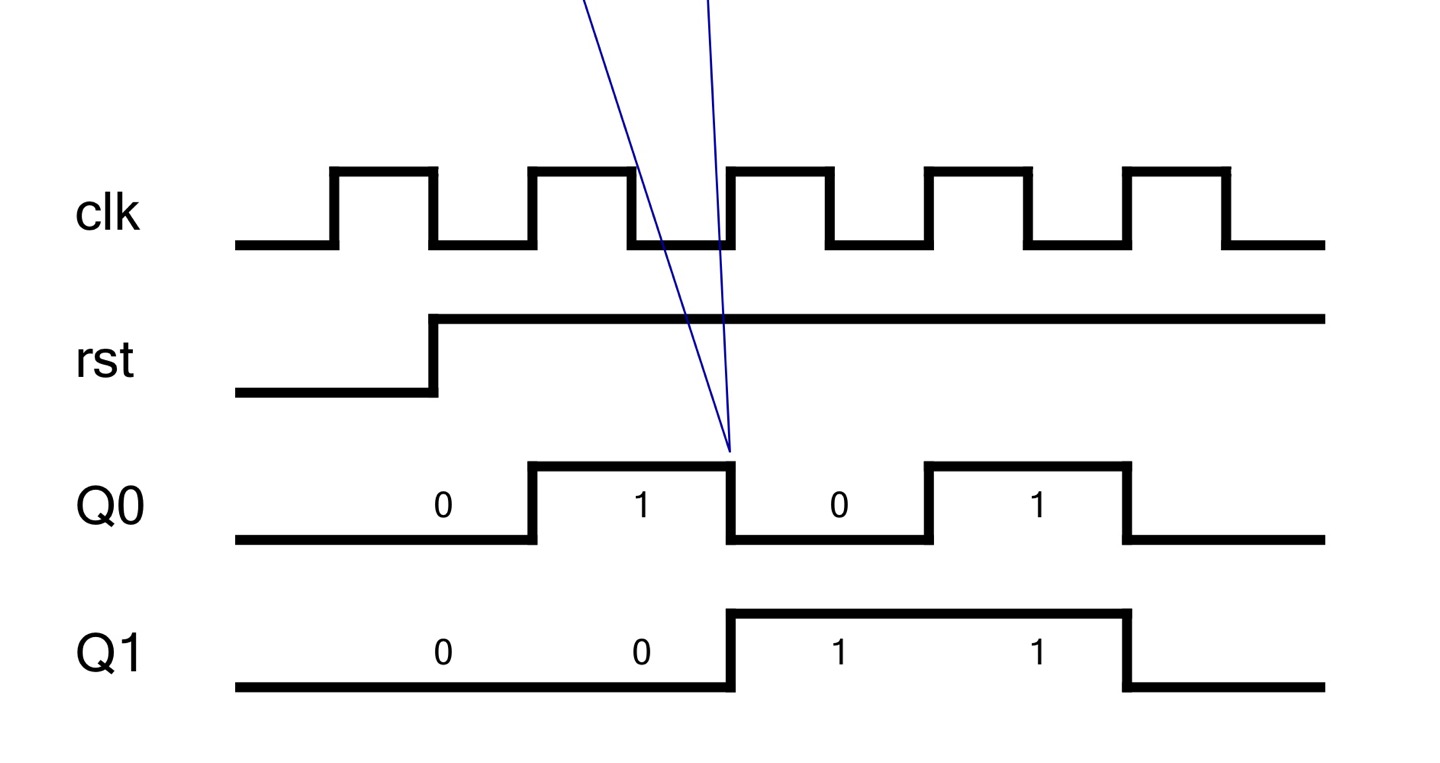

< 비동기 2비트 카운터 >

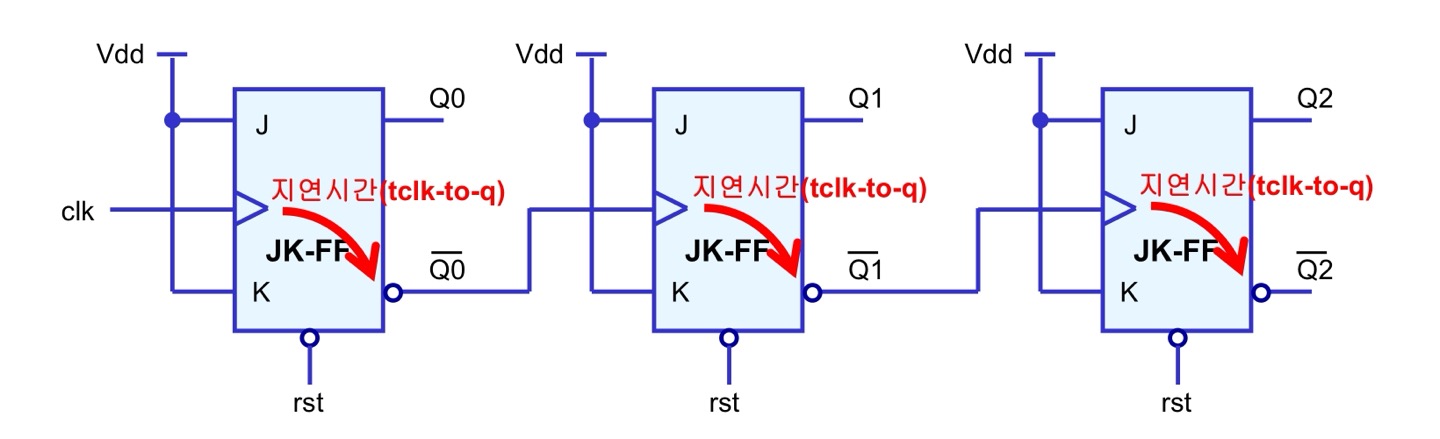

< 비동기 3비트 카운터 >

- 비동기 회로의 문제점 중 하나인 지연시간이 포함된다.

< 비동기 카운터의 단점 >

- 원인 : 카운터의 모든 플립플롭이 동시에 변하지 않는다.

- 단점 : 변하는 중간에 다른 값들이 섞여 있어 잘 못 사용될 우려가 있다.

지연시간 때문에 clock속도가 빠를 경우 사용하기 어렵다.

- 해결책 : 동기 카운터를 사용한다. F/F의 clock단자에는 항상 clock만을 연결하는 동기식 설계가 바람직하다.

< FSM(Finite State Machine)의 개요 >

FSM(한정된 상태를 갖는 머신)

- Counter(계수기)

- Clock divider(클럭 분주기)

- FSM

Register(레지스터)

- 플립플롭의 모임

- Shift register

- Parallel register

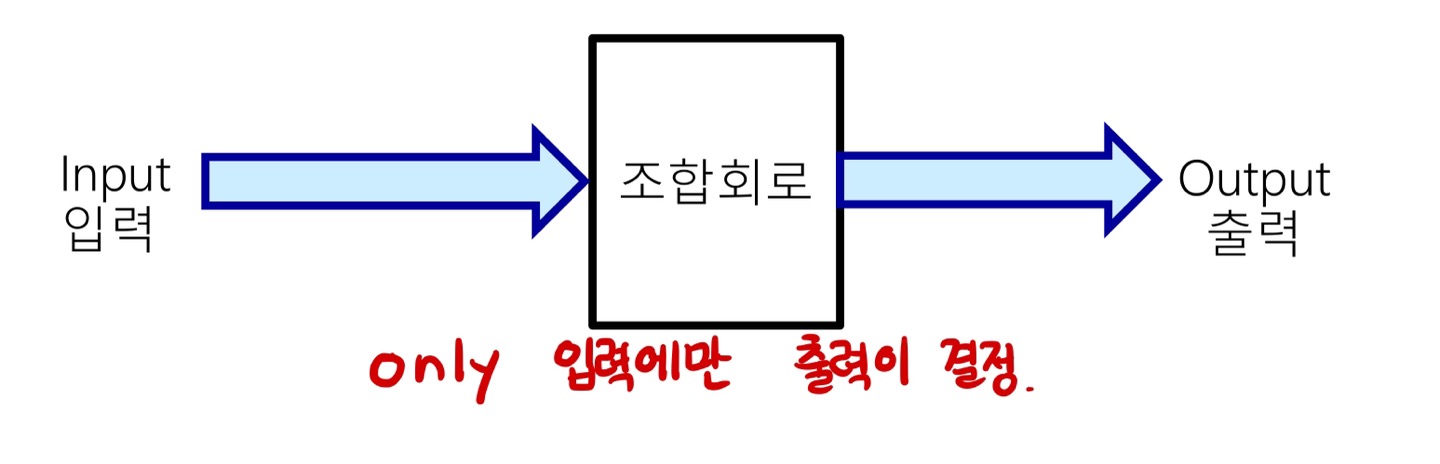

< FSM 타입의 회로 >

- 출력이 입력뿐 아니라 현재상태도 고려해 출력된다.

- 상태 레지스터에서 현재 상태를 저장한다.

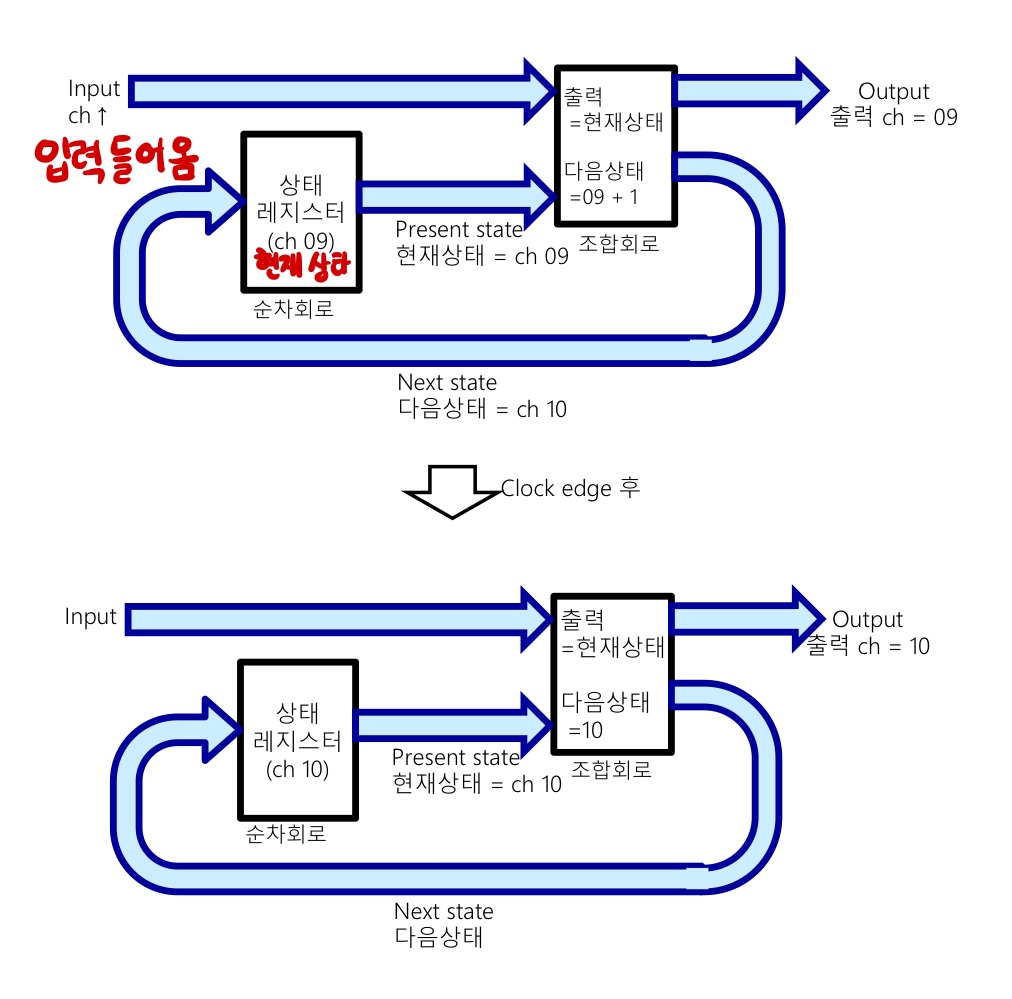

< FSM의 예(TV Channel 버튼)

채널 up 버튼을 눌렀을 때

- 현재 상태가 3이라면 다음 상태는 4

채널 down 버튼을 눌렀을 때

- 현재 상태가 3이라면 다음 상태는 2

즉, 다음 상태는 입력과 현재상태에 의해 결정되고 출력은 현재상태를 바로 출력으로 사용한다.(무어머신)

현재상태를 저장하는 순차회로로만 가능하며 조합회로로는 불가능하다.

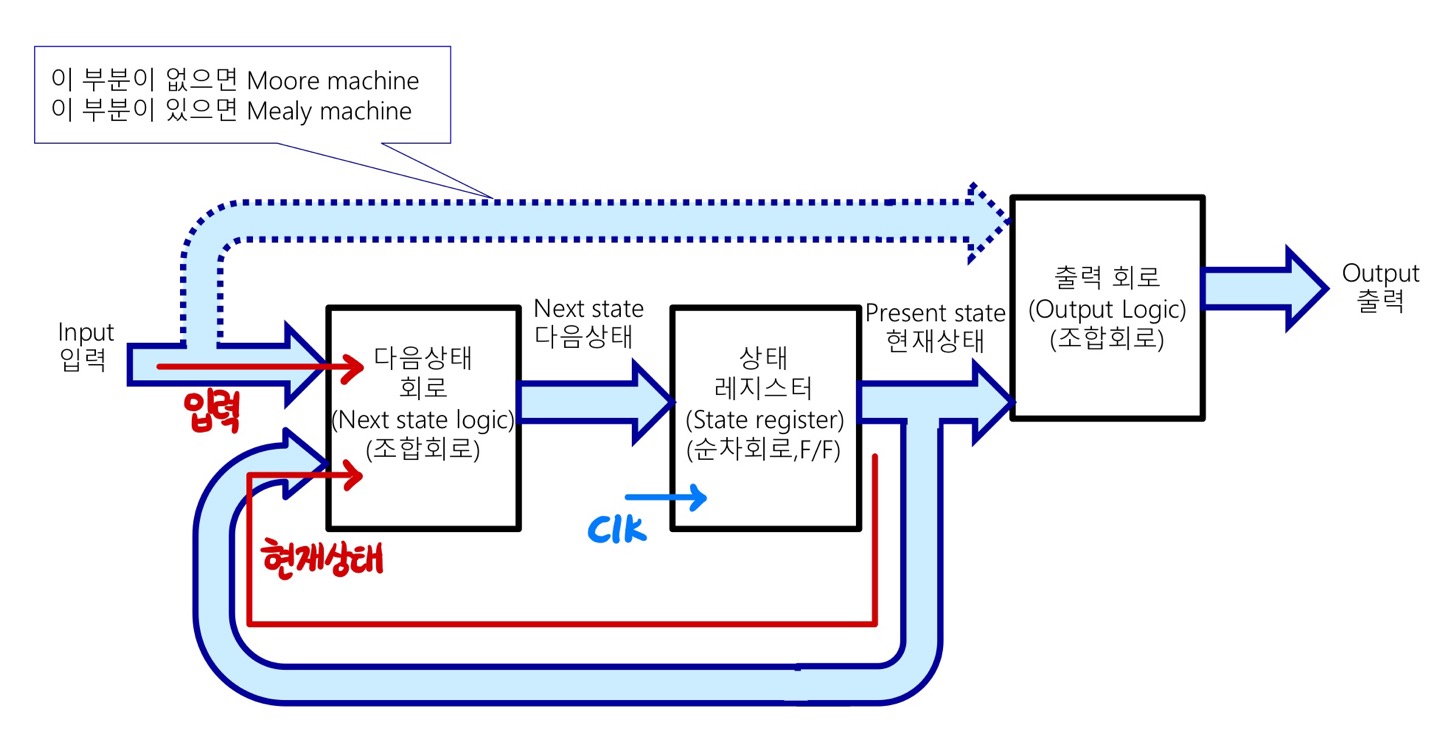

< 밀리 머신과 무어 머신 >

밀리 머신 : 출력이 현재상태 + 입력

무어 머신 : 출력이 현재상태

< FSM의 개념 >

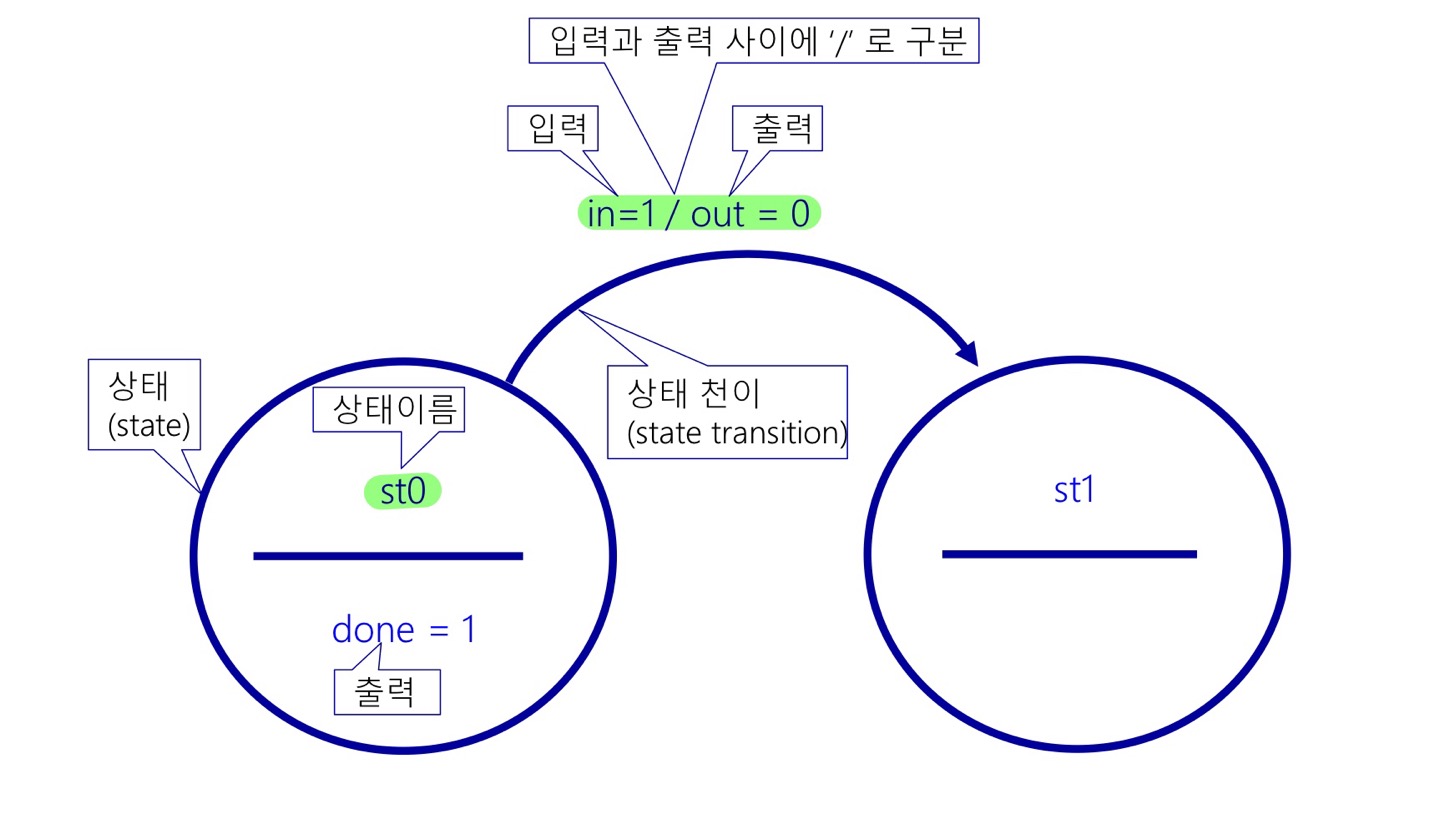

FSM(Finite State Machine)

- 유한한 개수의 상태를 가지고 있으며

- 입력과 현재상태에 따라 다음 상태가 결정되고

- (입력과) 현재상태에 따라 출력이 결정되는 머신

< FSM 세부 블록 >

Next state logic(조합 회로)

- 입력 + 현재상태 -->> 조합회로 -->> 다음상태

State register(순차회로, F/F, 현재 상태를 저장)

- 다음상태 -->> clock edge에서 저장 -->> 현재상태

Output logic(조합회로)

- Moore machine의 경우 : 현재상태 -->> 조합회로 -->> 출력

- Mealy machine의 경우 : 입력 + 현재상태 -->> 조합회로 -->> 출력

< 상태 다이어그램 예 (TV Channel 버튼) >

< 상태 다이어그램의 일반적인 표기법 >

< 상태표 (State table) >

< 파이프라인(Pipeline) 형태의 회로 >

'Computer Architecture > 논리회로' 카테고리의 다른 글

| [14] CH8 순차논리회로 < 카운터 FSM 설계-2 > (0) | 2022.01.09 |

|---|---|

| [13] CH8 순차논리회로 < 카운터 FSM 설계 > (0) | 2022.01.09 |

| [11] CH8 순차논리회로 < 플립플롭(Filp-Flops) > (0) | 2022.01.08 |

| [10] CH8 순차논리회로 < 래치(Latch) > (0) | 2022.01.06 |

| [9] CH7 조합논리회로 < 3상태 버퍼 > (0) | 2022.01.05 |

포스팅이 좋았다면 "좋아요❤️" 또는 "구독👍🏻" 해주세요!

![[14] CH8 순차논리회로 < 카운터 FSM 설계-2 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FcSZJca%2Fbtrp6xte67u%2FAAAAAAAAAAAAAAAAAAAAAA3WkubiVvX6UwnmE5ve4iu5iExh190X0rRPqtrRG9eT%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3D62jaCUH4WT5R2JTMuxdRBFqJp5o%253D)

![[13] CH8 순차논리회로 < 카운터 FSM 설계 >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbpKnYD%2Fbtrp8q0XhHR%2FAAAAAAAAAAAAAAAAAAAAAAmZXsgqbZq0aKjzTvXiWMMfGo5Q8lQScRZteusZVK21%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DqZyRLxz4GN9f70Fdf5x56OG7Og8%253D)

![[11] CH8 순차논리회로 < 플립플롭(Filp-Flops) >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FbSpzd8%2Fbtrp6RRRSqe%2FAAAAAAAAAAAAAAAAAAAAAE58-e6Su4EN3VmmPF2kqop2yThhFyKlmQuiAgM2Eb3a%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DxtiSIJCNX0rRgPvZ7Hzki6CarKM%253D)

![[10] CH8 순차논리회로 < 래치(Latch) >](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FclZOgr%2Fbtrp086FYsW%2FAAAAAAAAAAAAAAAAAAAAAOyoBYG6P-w7o-RssA8IUF2GfVe5d4amTZPwvFMGHIbl%2Fimg.jpg%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1777561199%26allow_ip%3D%26allow_referer%3D%26signature%3DW8isNOMQseje2De9dfaVJNWwOsw%253D)